芯片概述

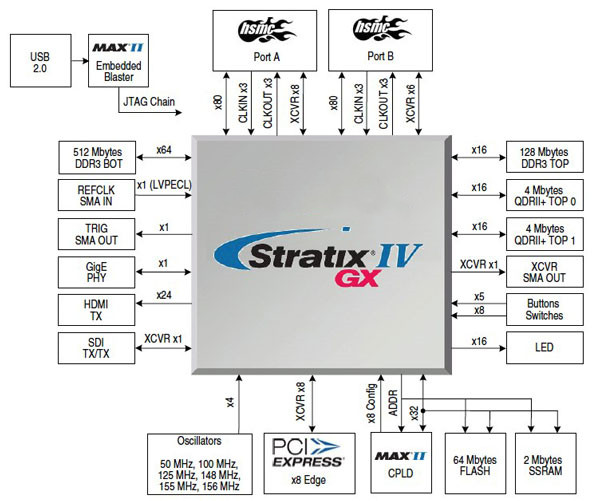

Stratix® IV 高密度、高性能 FPGA 具有前所未有的系统带宽和功率效率,适用于高端应用,您可借其实现彻底地创新。Stratix IV 系列器件共有三种优化型号,可满足不同的应用需求。Stratix IV E (增强型) FPGA—有813,050个逻辑单元(LE),33,294千位(Kb)RAM和1,288 18x18 位乘法器。Stratix IV GX 收发器 FPGA—有多达531,200个LE,27,376 Kb RAM和1,288 18x18位乘法器,并配有48个基于时钟数据恢复(CDR)的8.5Gbps全双工收发器。Stratix IV GT—有多达531,200个LE,27,376 Kb RAM和1,288 18x18位乘法器,并配有48个基于CDR的11.3Gbps全双工收发器。

芯片参数

EP4SGX110HF35I3G

LAB/CLB 数:4224

逻辑元件/单元数:105600

总 RAM 位数:9793536

I/O 数:488

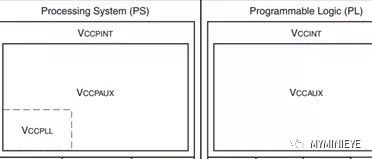

电压 - 供电:0.87V ~ 0.93V

安装类型:表面贴装型

工作温度:-40°C ~ 100°C(TJ)

封装/外壳:1152-BBGA,FCBGA

供应商器件封装:1152-FBGA(35x35)

EP4SGX110HF35C4G、EP4SGX110HF35C3G

LAB/CLB 数:4224

逻辑元件/单元数:105600

总 RAM 位数:9793536

I/O 数:488

电压 - 供电:0.87V ~ 0.93V

安装类型:表面贴装型

工作温度:0°C ~ 85°C(TJ)

封装/外壳:1152-BBGA,FCBGA

供应商器件封装:1152-FBGA(35x35)

Stratix IV 器件系列特性:

■ Stratix IV GX 和 GT 器件中多达 48 个全双工基于 CDR 的收发器分别支持高达 8.5 Gbps 和 11.3 Gbps 的数据速率

■ 支持流行串行物理层功能的专用电路协议,例如 PCI Express (PCIe) (PIPE) Gen1 和 Gen2、Gbps 以太网 (GbE)、串行 RapidIO、SONET/SDH、XAUI/HiGig、(OIF) CEI-6G、SD/HD/3G-SDI、光纤通道、SFI-5 和因特拉肯

■ 具有嵌入式 PCIe 硬核 IP 块的完整 PCIe 协议解决方案,实现 PHY-MAC 层、数据链路层和事务层功能

■ 可编程发送器预加重和接收器均衡电路补偿物理介质中与频率相关的损耗

■ 典型物理介质连接 (PMA) 功耗为 100 mW,在3.125 Gbps 和 135 mW,每通道 6.375 Gbps

■ 每台设备 72,600 到 813,050 个等效 LE

■ 7,370 至 33,294 Kb 的增强型 TriMatrix 内存,由三个 RAM 块组成实现真正的双端口内存和 FIFO 缓冲区的大小

■ 高速数字信号处理 (DSP) 模块可配置为 9 x 9 位,12 个 12 位、18 个 18 位和 36 个 36 位全精度乘法器,频率高达 600 MHz

■ 多达 16 个全局时钟 (GCLK)、88 个区域时钟 (RCLK) 和 132 个外设每个设备的时钟 (PCLK)

■ 可编程电源技术,在最大限度地提高设备性能的同时最大限度地降低功耗表现EP4SGX230FF35I3N

■ 多达 1,120 个用户 I/O 引脚排列在 24 个模块化 I/O bank 中,支持广泛的一系列单端和差分 I/O 标准

■ 支持高速外部存储器接口,包括 DDR、DDR2、多达 24 个模块化的 DDR3 SDRAM、RLDRAM II、QDR II 和 QDR II+ SRAMI/O 银行EP4SGX230FF35I3N

■ 带串行器/解串器 (SERDES) 的高速 LVDS I/O 支持,动态相位对齐 (DPA) 和数据速率高达 1.6 Gbps 的软 CDR 电路

■ 支持源同步总线标准,包括 SGMII、GbE、SPI-4第 2 阶段(POS-PHY 级别 4)、SFI-4.1、XSBI、UTOPIA IV、NPSI 和 CSIX-L1

■ Stratix IV E 器件的引脚布局,旨在允许从Stratix III 到 Stratix IV E,对 PCB 的影响最小

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

暂无评论