凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片 IC流片时,工程师如何检查设计规则?

为确保电子产品的顺利上市,集成电路(IC)不能缺少“流片阶段”,在流片前,设计规则检查(DRC)与版图与电路图一致性检查(LVS)是确保芯片成功制造并符合预期功能的关键步骤。

1、电容长宽比检查

确保电容长宽比合理,避免电场分布不均,影响性能。

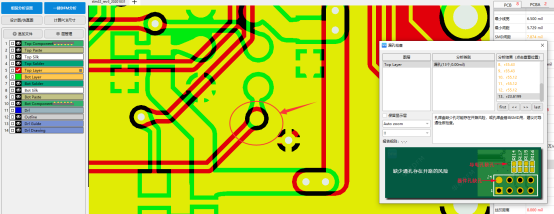

2、接地孔优化

充分利用版图空位添加接地孔,预防闩锁效应,提高电路稳定性。

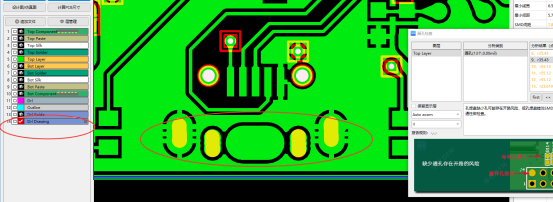

3、天线效应监控

针对大面积金属连接至栅极的情况,进行天线效应检查,必要时采取跳线措施,防止制造过程中因电荷累积导致栅氧化层击穿。

4、全面仿真验证

包括功能仿真、布局布线后仿真及时序仿真,且需带IO接口进行,确保设计在所有阶段均符合预期。

5、使用最新工艺文件

在SMIC等代工厂流片时,确保采用Technologyfile目录下最新的工艺文件,避免使用PDK中的过时版本。

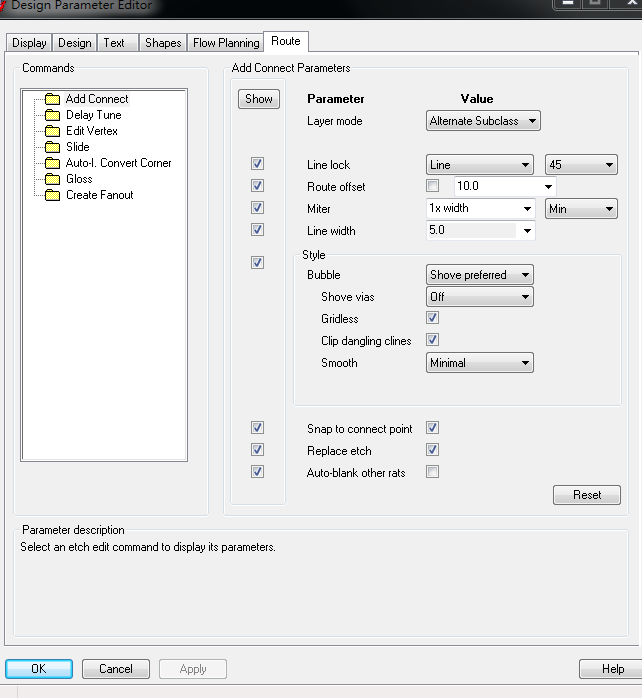

6、更新DRC与LVS文件

流片前访问Foundry网站,下载最新的DRC与LVS检查文件,特别是65nm及以下工艺需额外进行DFM(可制造性设计)检查。

7、数模混合版图验证

数模整合后,通过gds文件导入导出循环检查,确认版图层次无丢失,并执行严格的DRC与LVS检查。

8、第三方IP的DRC合规性、

若发现标准单元或第三方IP存在DRC违规,立即与IP供应商沟通,确保IP库功能正确且能通过最新的DRC检查。

9、芯片标识LOGO

每块芯片设计均需包含特定LOGO,建议格式为“芯片名称_流片日期”,如“ADC_080618”,以便于追踪与识别。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论