前一段时间有个兄弟问了个问题,把我问住了,问题是这个:

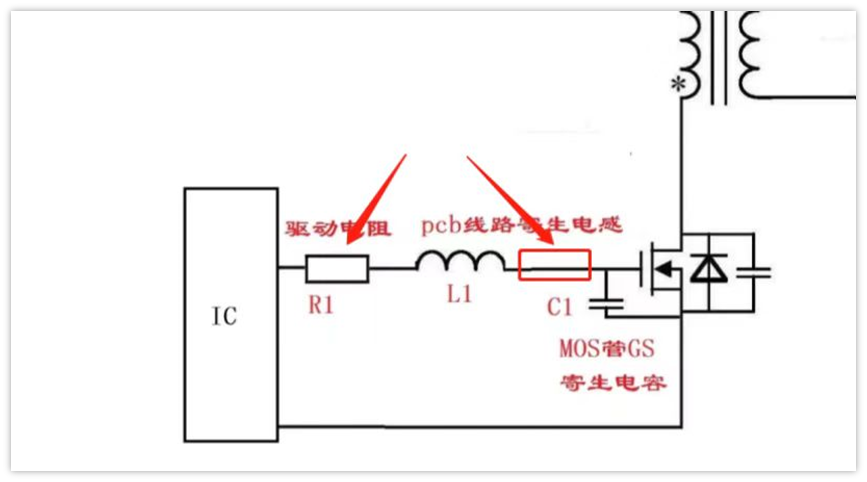

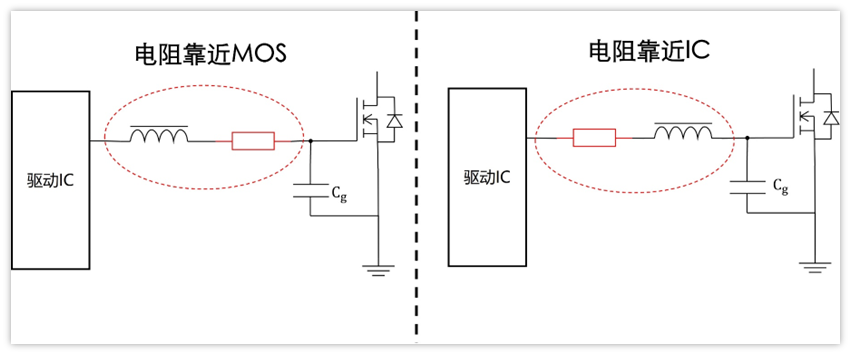

如上图,串联的电阻R1到底是放在靠近IC端,还是靠近MOS端?(注意,图中的L1是走线寄生电感,并不是这里放了个电感器件)

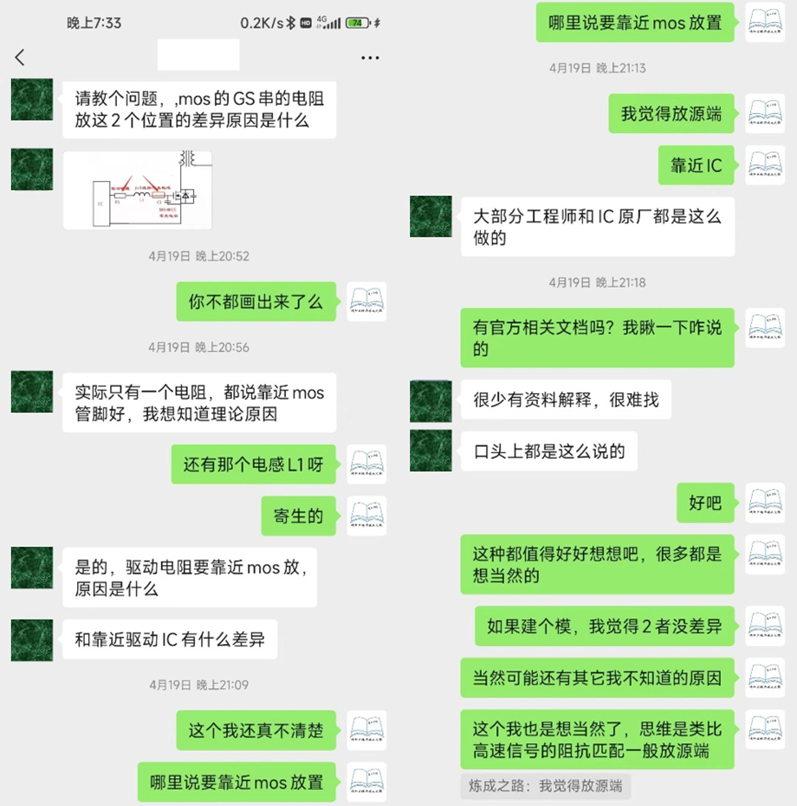

我们具体沟通的情况是这样的:

这位兄弟说大部分工程师和IC原厂都是这么做的,但是没有说为什么,我当时也不清楚。但是这个问题确实是个好问题,现实中的确存在。

任何一个问题都是提升技术的机会,所以,我记了下来,然后花时间看了看。

在这之前,为了让所有兄弟都能跟上节奏,那必须先得搞清楚这个串联的电阻是干什么用的。

简单说,这个串联的电阻就是抑制振荡用的,具体怎么回事,我以前专门写过文章,不知道的可以去瞅瞅——“LC串联谐振的意义-MOS管栅极电阻”

真实情况如何

首先,这位兄弟说大部分都是放靠近MOS端。关于这一点,我先去求证了下,看实际情况是否真是如此?

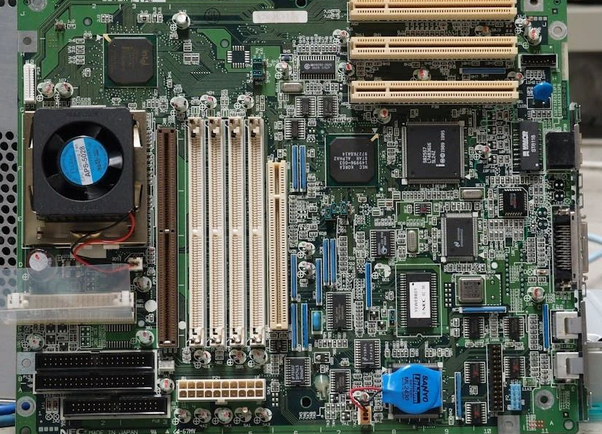

一般这种驱动MOS的电路,开关电源和电机驱动居多,因此,我就去找了这两类IC的厂商,去看看它们的demo板是怎么Layout的。

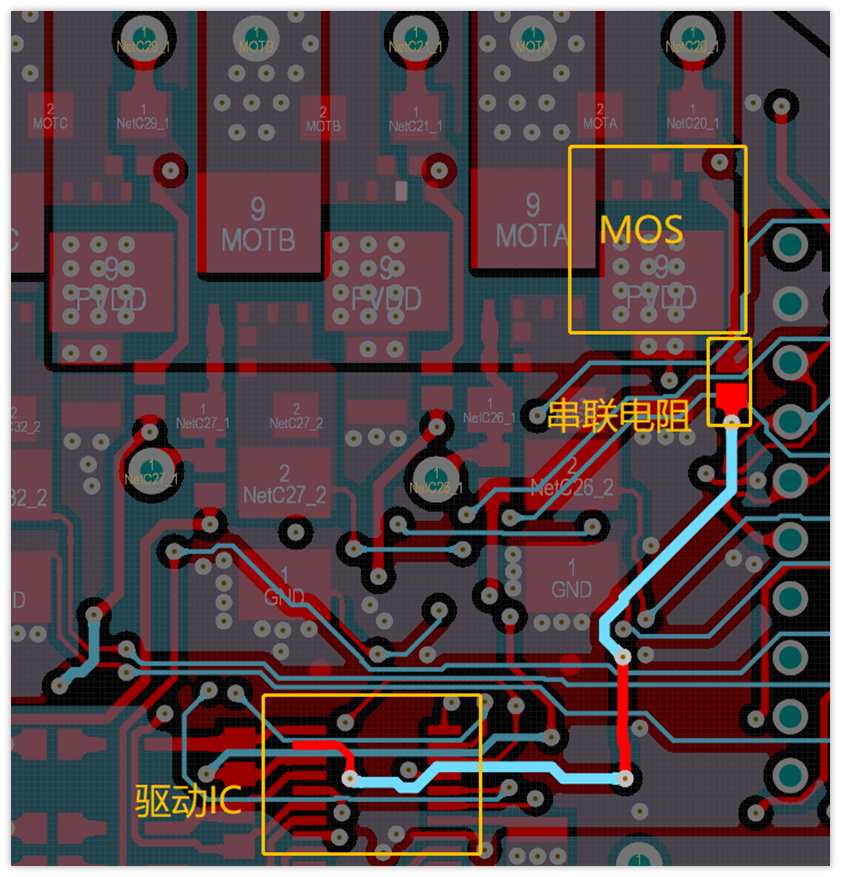

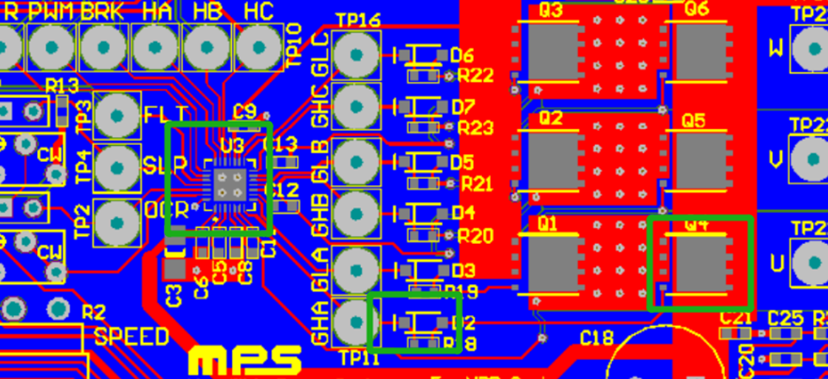

1、 TI的无刷电机驱动芯片DRV8300的demo板

Demo板硬件设计可以直接在Ti官网下载,如下图,可以看到,串联电阻是放置在MOS管端的。

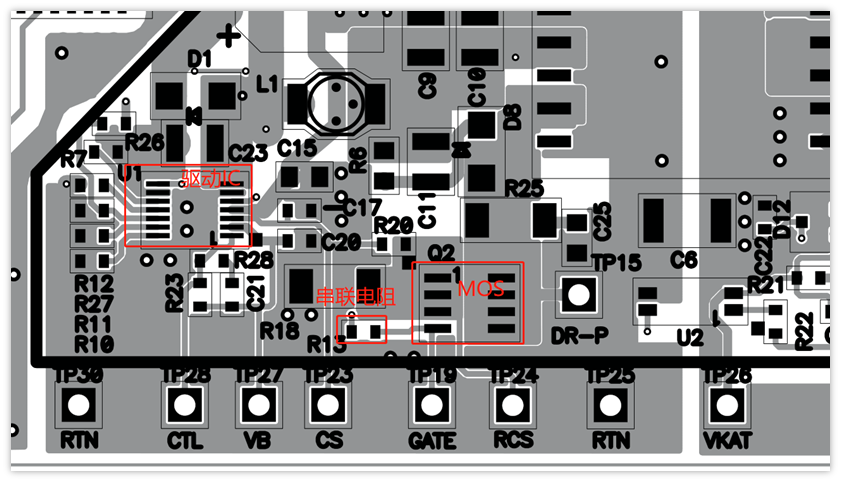

2、 Ti的POE方案TPS23753A的Demo板

原理图如下:

PCB如下图,串联电阻也是放置在靠近MOS管端。

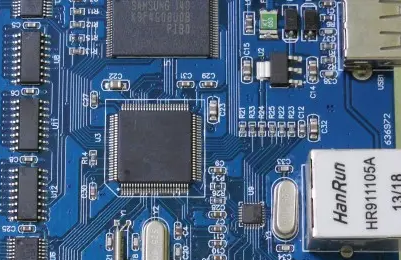

3、 MPS的无刷电机驱动芯片MP6535。

如下图,6个MOS的栅极串联电阻R18,R19,R20,R21,R22,R23放置在中间。

从走线长度看,Q1,Q2,Q3串联的电阻离MOS较近,离驱动IC较远。Q4,Q5,Q6串联的电阻在MOS和驱动IC中间。

就上面3个例子来说,兄弟说的“大部分情况栅极串联电阻靠近MOS管放置”确实是属实的。

那我聊天记录里面说的“放源端比较好,就像高速信号的阻抗匹配放源端”,这一点又是考虑了什么呢?

是否需要考虑阻抗匹配

考虑到阻抗匹配,那就是将信号看作是高速信号,那么到底栅极驱动信号是不是高速信号呢?

一般来说,高速信号的认定规则是这样的:信号的上升沿小于6倍的传输延时。那我们大致算一下就知道是不是高速信号了。

PCB上信号传输速度为6inch/ns,也就是0.1524m/ns

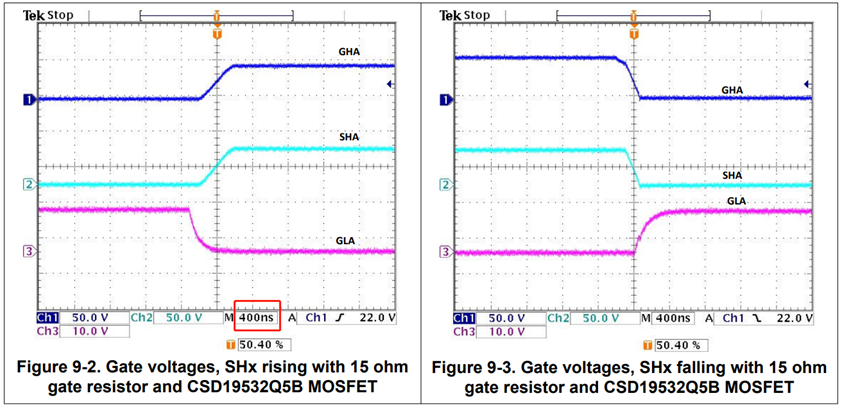

以DRV8300为例子,可以从手册中看到栅极驱动信号波形,如下图的GHA就是:

上升沿大概是400ns,如果要将其看成是高速信号,那么需要满足公式:

400ns<6*l>

算得L>10.16m

显然,我们的栅极走线远小于10m,所以栅极走线不用看成是高速信号线,也就说不用考虑阻抗匹配的问题,用集总参数模型分析即可。

一般情况下,我们的栅极走线长度不会超过10cm。那么当走线是10cm时,如果要将其看成是高速信号,那么对应的Tr<3.9ns<>。

我印象中,MOS管驱动电路,上升时间都不会这么小,所以,都是不用将其考虑成高速信号的了,也就是说从这个维度考虑,这个电阻不必放置到靠近源端IC。

放置到靠近MOS端有什么好处

既然不必放到靠近IC,那么放到靠近MOS有什么好处呢?

其实从上面两个模型看来, 对于MOS栅极来说,它们收到的信号没有任何的差别。

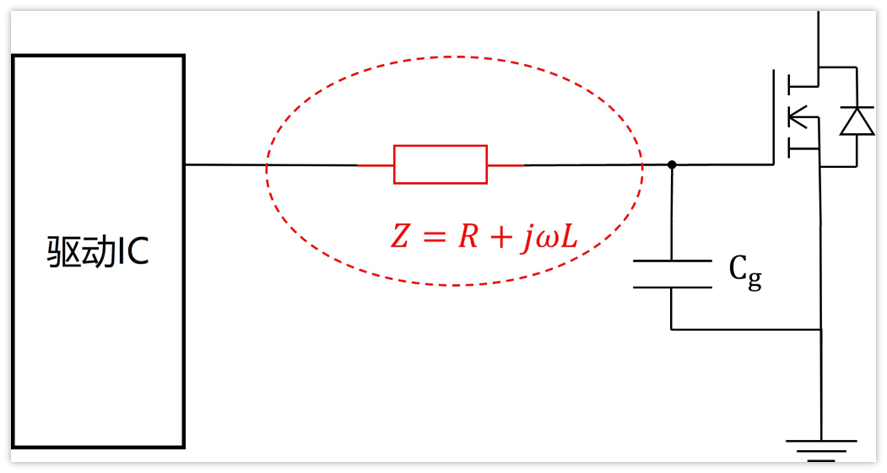

为什么这么说呢?因为电感和电阻始终是串联的,如果把它们看成一个整体,阻抗就是R jwL,对于整个电路来说完全是相同的,等效为下面这个:

所以,我不觉得串联电阻靠近MOS放置有什么特别的作用。

小结

以上就是,我目前对于MOS管栅极串联电阻放在哪儿的看法。

我觉得放在哪里无所谓,靠近MOS,靠近驱动IC都行,放中间也行,重要的总的走线长度要短(这一点在很多手册中都有提到,主要为了降低走线寄生电感)。

当然了,极有可能有其它我还没考虑到的因素,所以我觉得放哪儿都行是不对的。

暂无评论