简介

在生成式人工智能、高性能计算 (HPC) 和数据中心的推动下,人们对计算能力的需求不断增长,这也刺激了对先进 CMOS 工艺和封装技术的需求。为满足这一日益增长的需求,半导体行业正在推动到 2030 年实现万亿晶体管三维集成电路(3DIC)系统级封装(SiP)解决方案。本文将探讨台积电推动采用chiplet的力量、先进的 CMOS 技术、特定领域芯片优化、封装创新、专用芯片和设计启用工作。

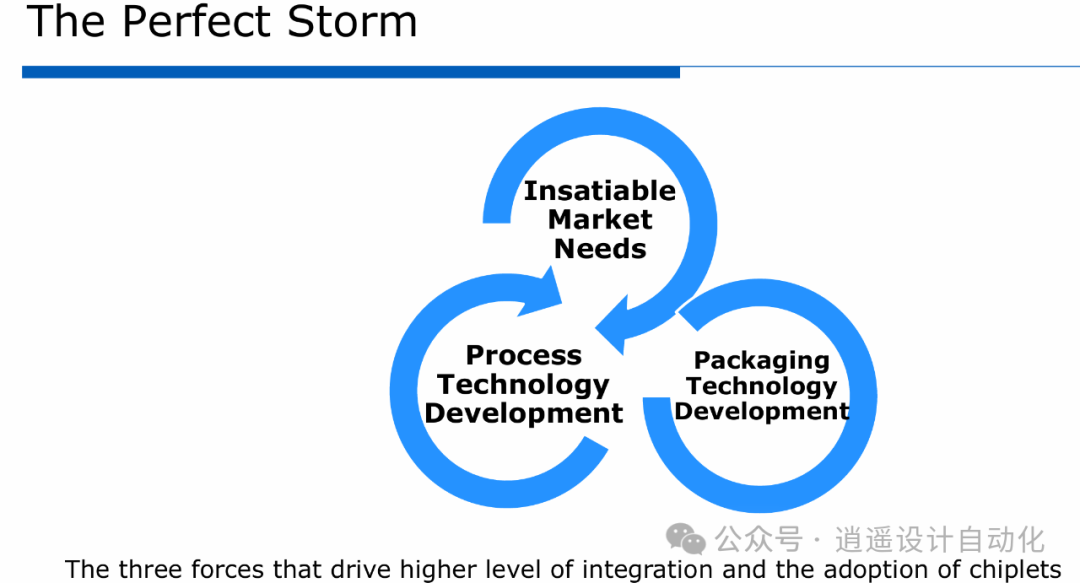

推动采用Chiplet的力量

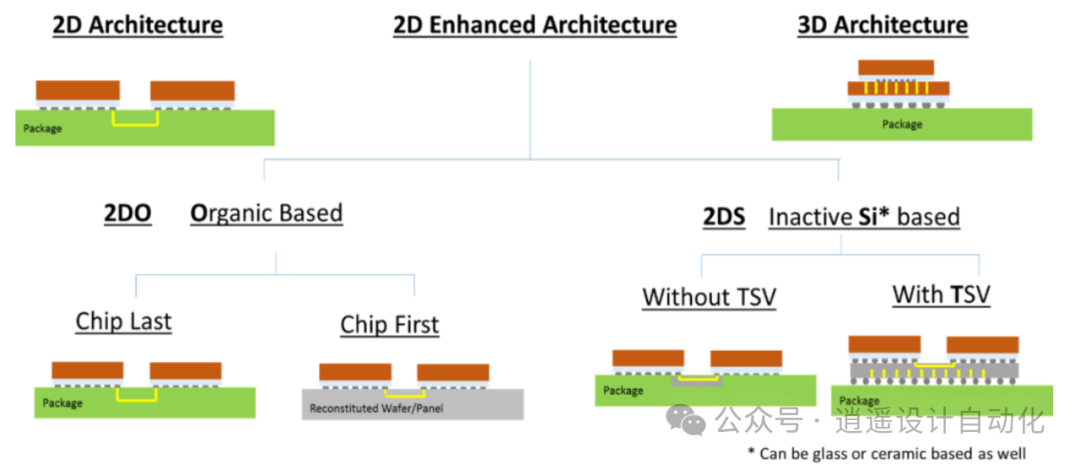

推动采用chiplet和更高集成度的有三股关键力量:永不满足的市场需求、工艺技术发展和封装技术进步。人工智能的兴起以及对更多计算、内存和 I/O 带宽的需求,推动了对工作负载优化、架构多样化和异构集成的需求。与此同时,CMOS 规模不断扩大,导致晶体管增多,工艺复杂性增加。晶圆上封装(WoW)和芯片上封装(CoW)等先进封装技术为集成计算、内存和 I/O 组件提供了有效途径。

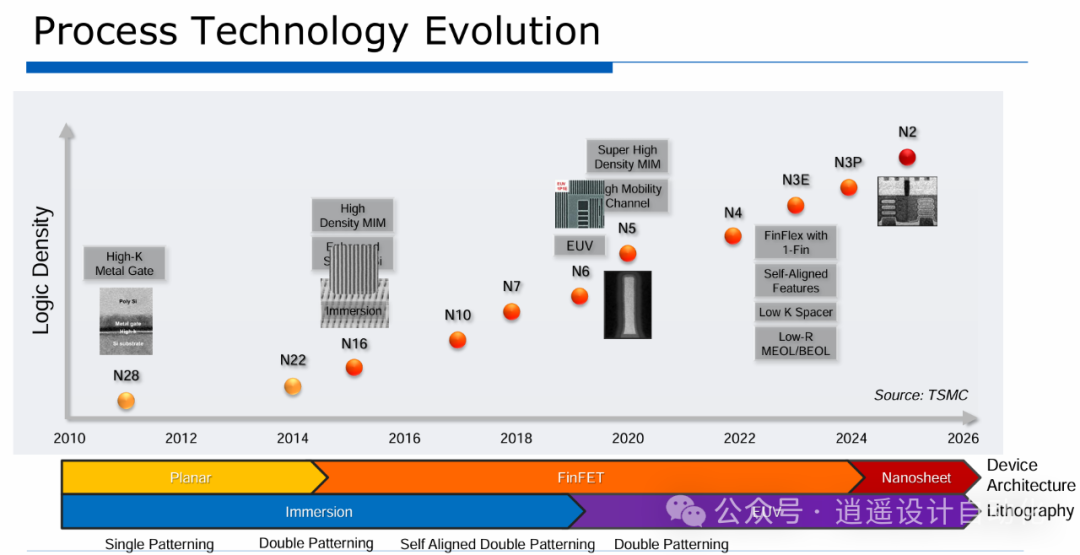

先进的 CMOS 技术

台积公司的工艺技术路线图展示了对逻辑密度扩展的不懈追求,其中包括 FinFET、纳米片晶体管等创新技术,以及互补场效应晶体管 (CFET) 和二维transition metal dichalcogenides (TMDs).等新兴晶体管架构。每个节点在性能、功耗和面积(PPA)方面都有显著改善,从而实现了高能效计算解决方案。

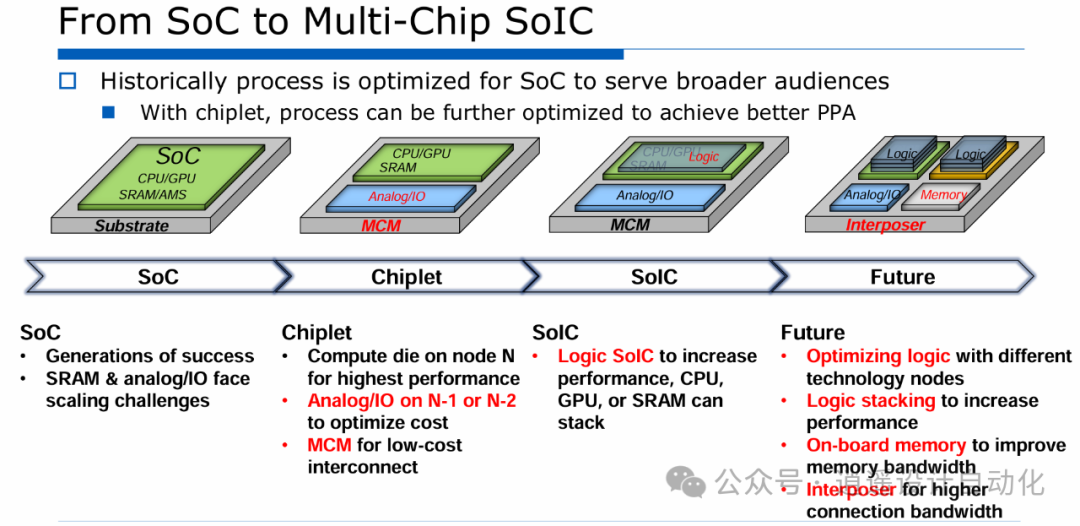

特定领域Chiplet优化

从系统级芯片(SoC)过渡到系统集成芯片(SoIC),可实现特定领域芯片的优化。计算芯片可以利用最新的工艺节点来优化 PPA,而 SRAM 和模拟/IO 芯片则可以利用更成熟的节点来平衡成本和产量。这种方法可根据采用时间、芯片尺寸、工艺节点、缺陷密度和 IP 可用性对芯片进行独立优化。

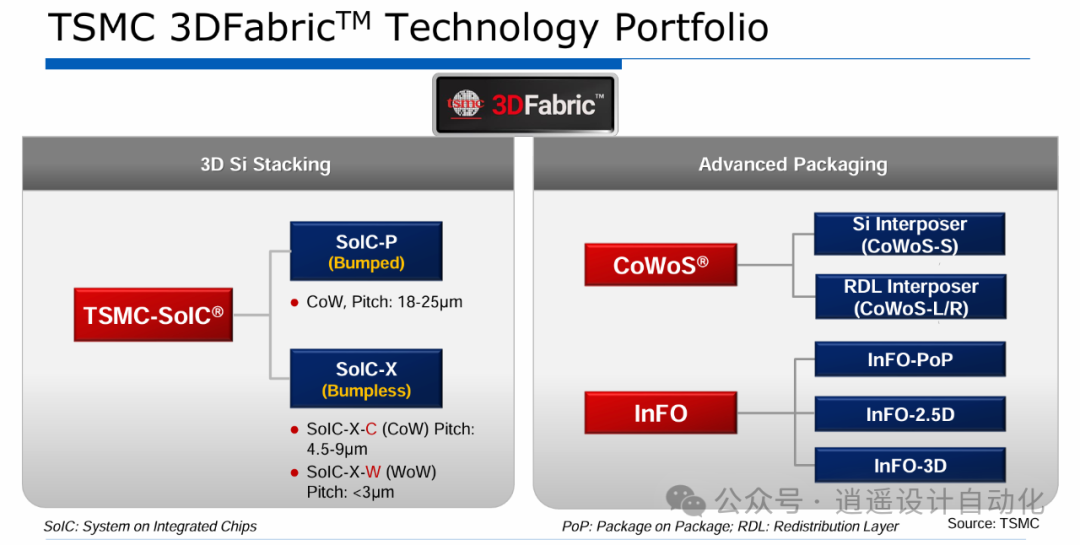

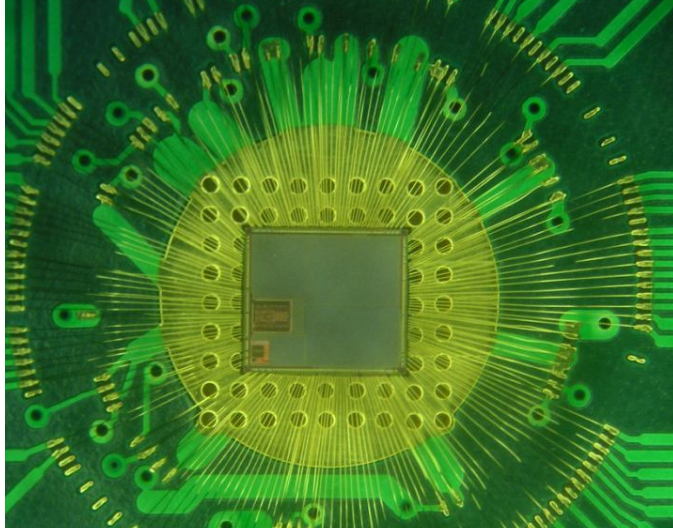

先进的封装技术

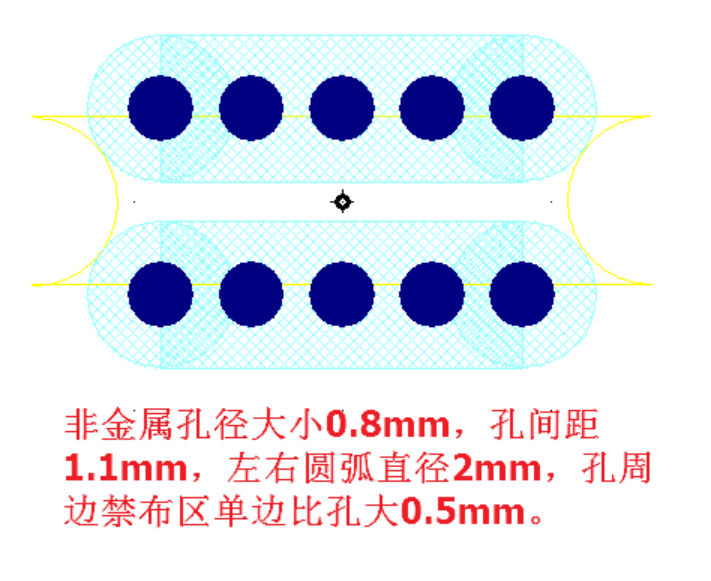

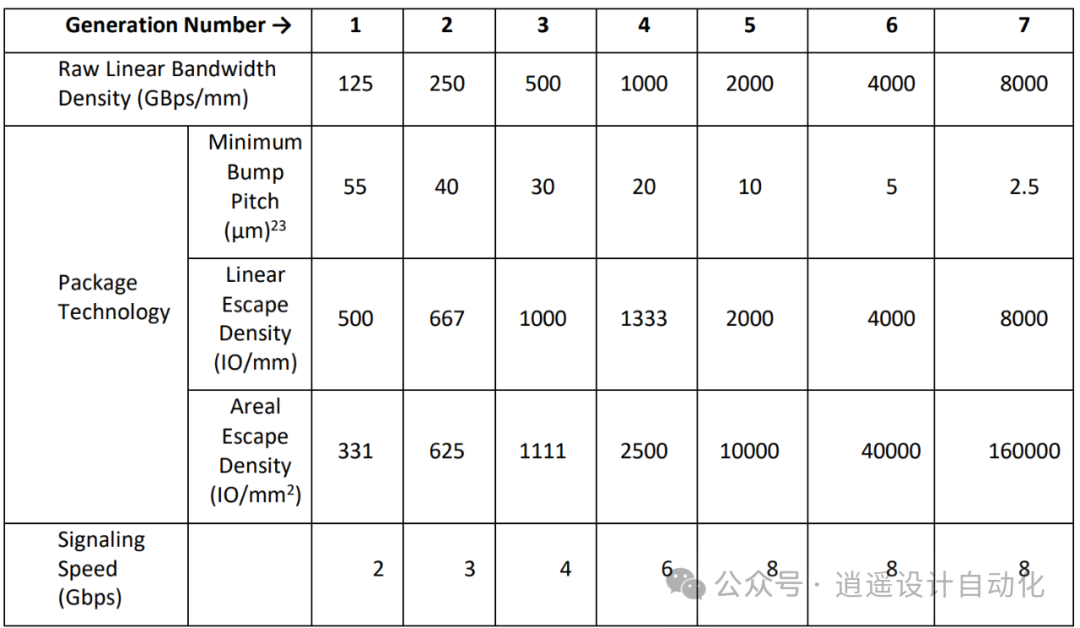

台积公司的 3DFabric™ 产品组合提供全面的先进封装解决方案,包括 CoWoS(基板上芯片)、InFO(集成扇出)和 SoIC(系统集成芯片)。这些技术实现了高密度芯片到芯片互连,提供了前所未有的带宽密度和能效。

平台解决方案专用芯片

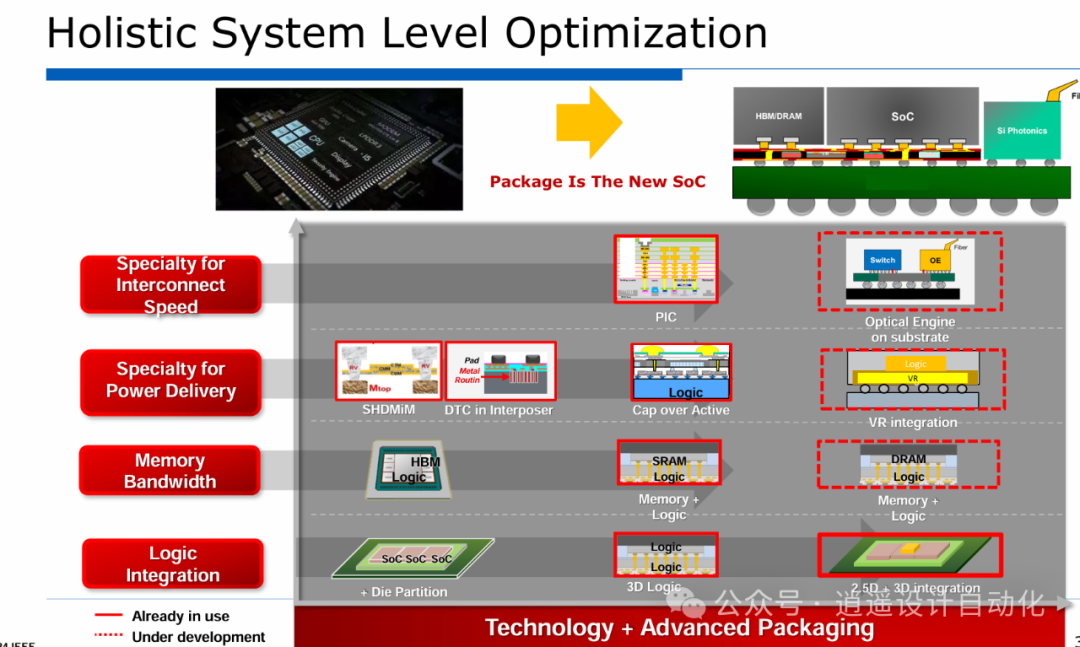

封装正在成为新的 SoC,技术和先进的封装解决方案实现了专业化和优化。存储器/逻辑芯片堆叠、硅基光电子光电共封装器件(CPO)和集成稳压器(IVR)等新兴解决方案正在推进整体系统级优化。

内存带宽和互连创新

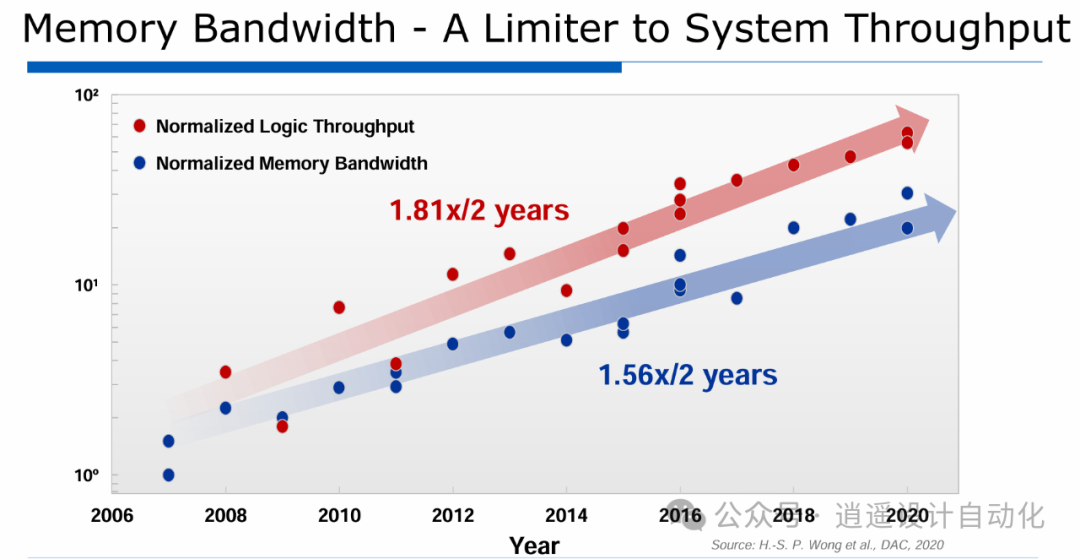

内存带宽已成为系统吞吐量的瓶颈,因为逻辑吞吐量的扩展速度快于内存带宽。三维堆叠 DRAM 和高带宽内存 (HBM) 技术为这一挑战提供了解决方案,使内存带宽得到显著改善。

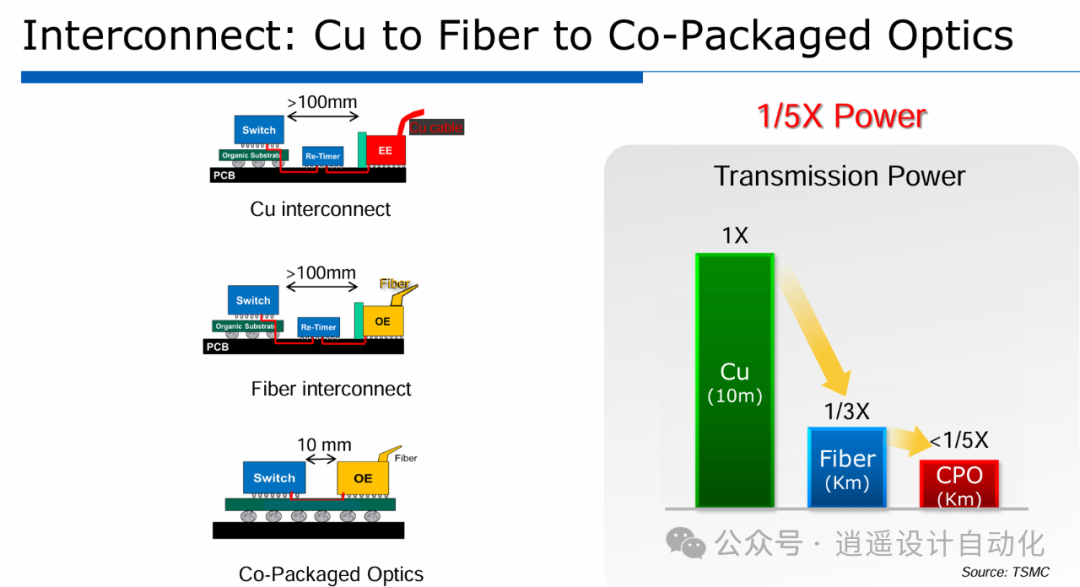

此外,业界正在见证从铜缆互连向光纤和光电共封装技术的过渡,从而降低功耗并在更远的距离上实现更高的带宽。

电力传输创新

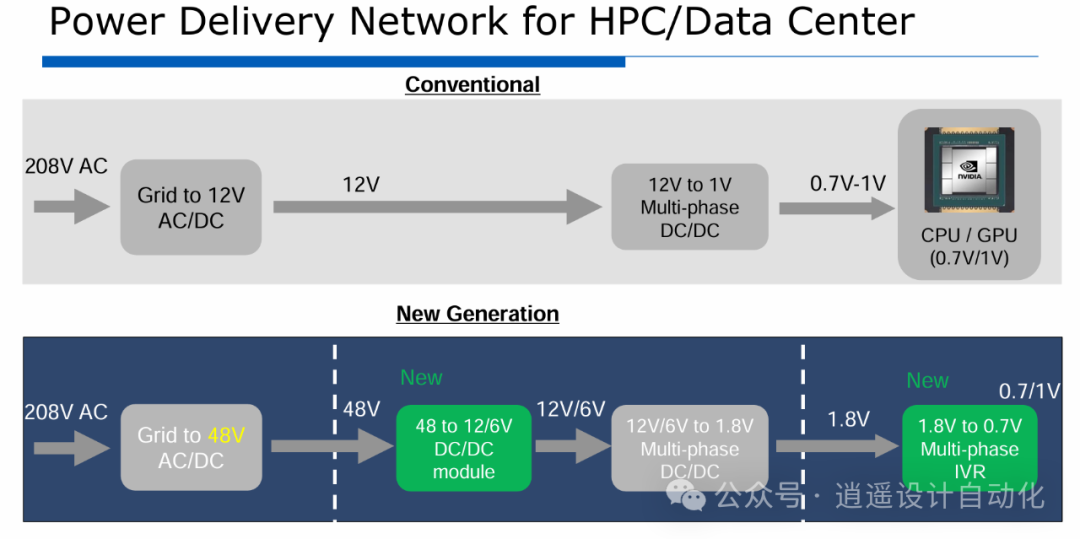

在数据中心和高性能计算系统中,电力传输网络正在经历一场变革。传统方法涉及从交流到直流的多个转换级,导致效率损失。新一代技术用交流电到较高直流电压(如 48V)的单级转换取代了多级转换,然后在靠近负载的地方进行分布式电压调节。这包括将电压调节器 (IVR) 作为芯片集成在封装内,从而降低输入电流并提高效率。

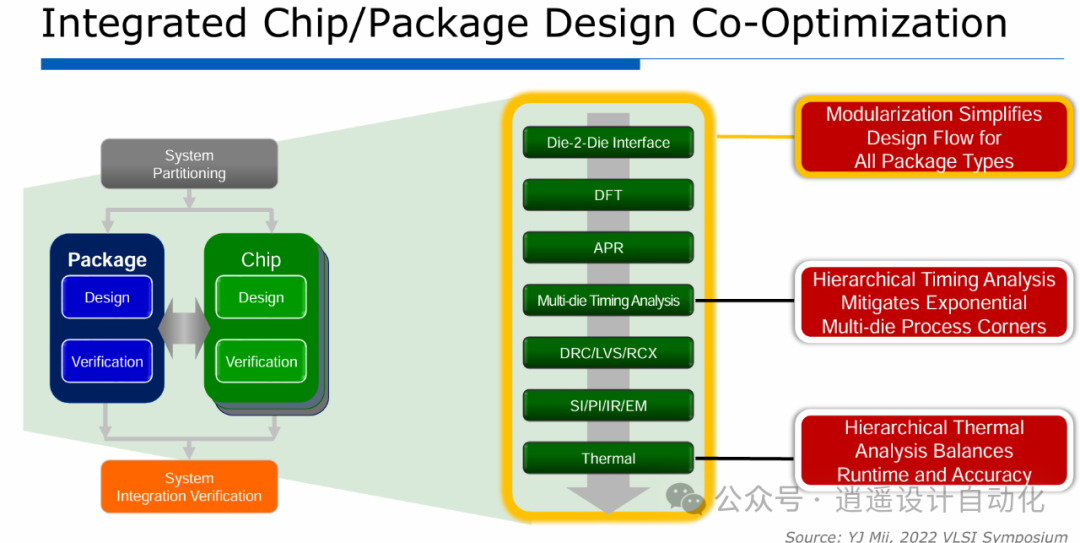

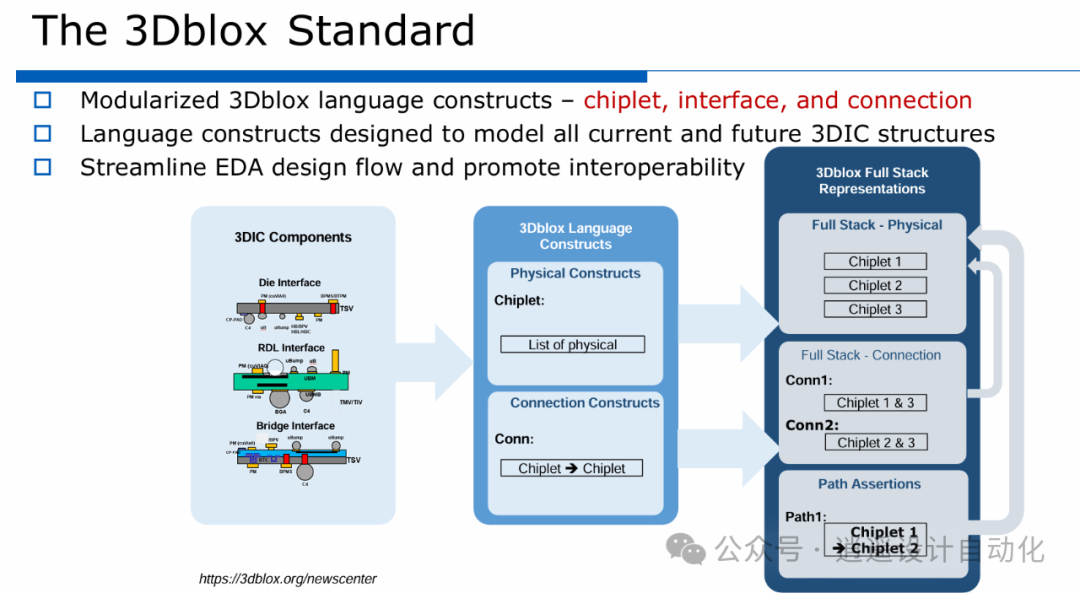

设计启用和生态系统

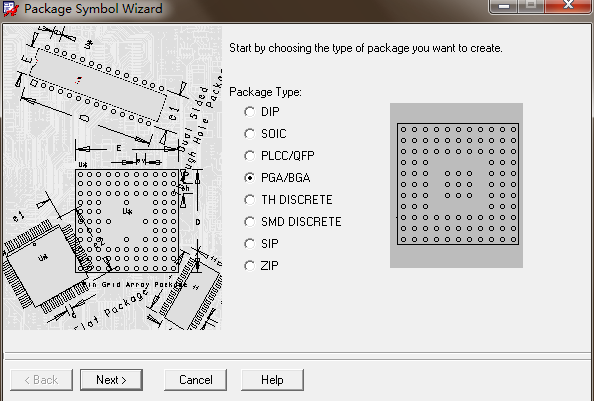

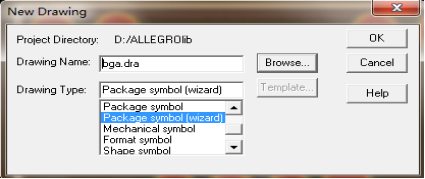

随着设计复杂度从 2D 增加到 2.5D/3D,一个紧密耦合的封装/芯片协同设计流程对于加快设计融合很重要。这需要 EDA 供应商、IP 提供商和半导体生态系统之间的合作。3Dblox 标准等倡议旨在简化 EDA 设计流程,并通过提供模块化语言结构来模拟当前和未来的 3DIC 结构,从而促进互操作性。

结论

对计算能力的不懈追求正在推动半导体行业到 2030 年实现万亿晶体管 3DIC 封装系统解决方案。先进的 CMOS 工艺、封装技术和设计支持工作正在汇聚在一起,以开启高性能、高能效和高集成度芯片系统的时代。行业生态系统在工艺、封装和设计方面的合作与创新将有助于实现这一里程碑,并满足生成式人工智能和高性能计算等新兴应用的无限需求。

暂无评论