凡亿教育-小叶

凡事用心,一起进步打开APP

公司名片射频电路如何做好电磁兼容性(EMC)设计?

随着无线射频技术高速发展,射频电路因为高频特性,在电磁兼容性(EMC)设计受到的阻碍越来越大,因此工程师必须要掌握射频电路的EMC设计技巧,以此确保射频电路在各种电磁环境中稳定工作,减少对其他电子设备的干扰。

1、印制导线宽度与长度优化

射频电路中,印制导线宽度应尽可能宽,以减少电感量,建议宽度不小于0.5mm。

缩短印制导线长度,特别是时钟信号和高速数据线,以减少电磁辐射和干扰。

2、布线策略

采用井字形网状布线结构,减少导线间的互感与分布电容。

避免长距离平行走线,以减少串扰。

信号线与地线、电源线交叉时,采用45度或更大角度交叉,减少干扰。

3、接地设计

射频电路应设计专用接地层,确保接地良好。

在敏感信号线之间设置接地印制线,抑制串扰。

高速信号线附近设置连续的地线,以屏蔽电磁干扰。

4、抑制电磁辐射

导线宽度和拐角设计应连续,避免突变,拐角大于90度。

时钟信号引线靠近地线回路,减少电磁辐射。

数据总线布线时,每两根信号线之间夹一根信号地线。

5、终端匹配

对于长距离传输线,如射频信号线,应在末端加接匹配电阻,以减少反射干扰。

匹配电阻阻值根据电路输出驱动电流和吸收电流决定。

6、差分信号线设计

射频电路中,差分信号线应成对布线,且距离保持不变。

差分线对中的PCB线应具有完全一致的阻抗和长度。

差分信号线应尽可能靠近,以减少EMI发射。

7、屏蔽与滤波

在射频电路周围设置屏蔽层,减少外部电磁干扰。

在输入输出端口添加滤波器,抑制高频干扰信号。

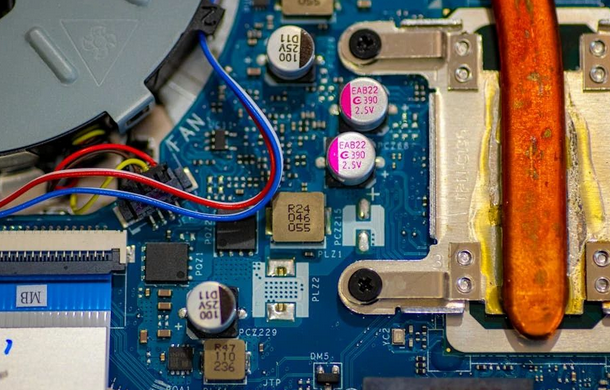

8、布局与元件选择

射频电路元件应紧凑布局,减少引线长度。

选择低噪声、高稳定性的元件,减少电磁干扰。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论