引言

随着半导体产业的发展,互补场效应晶体管(CFET)技术在推进未来逻辑技术发展方面展现出显著优势。本文将介绍栅极间距达到48纳米的单片CFET反相器的首次实现,该器件展现出高达1.2伏特的优异电压传输特性[1]。

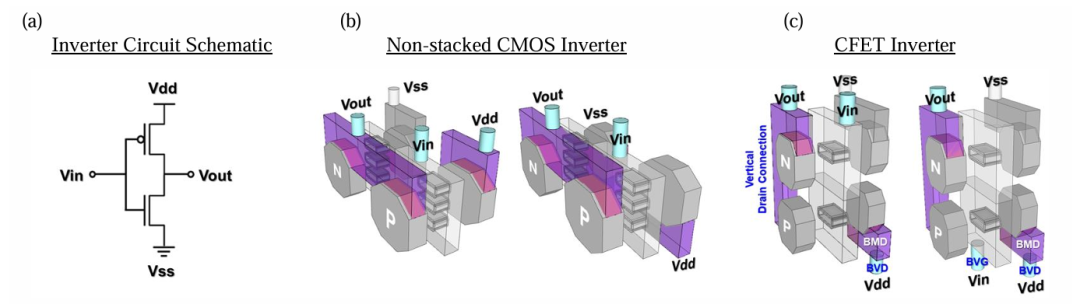

图1展示了从基本反相器电路原理图到先进CFET架构的演进过程,显示了从传统互补金属氧化物半导体(CMOS)到垂直堆叠设计的转变。

CFET技术的基本理念在于其创新的垂直堆叠方法,通过将n型场效应晶体管(nFET)和p型场效应晶体管(pFET)垂直排列而非水平排列。这种架构创新在不增加占地面积的情况下使晶体管密度提高一倍,从而提升功能性并改善功率效率。垂直集成为中间线(MOL)局部互连结构引入了新的范式,使其与传统CMOS技术有明显区别。

1

工艺架构与制造

CFET器件的制造工艺涉及一系列精密步骤,经过精心设计以实现最佳性能和可靠性。

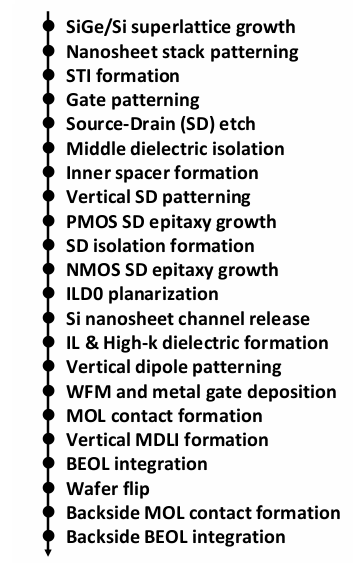

图2展示了在单个晶圆上制作n/p型场效应晶体管和反相器的完整单片CFET工艺集成步骤。

工艺始于锗硅/硅超晶格生长,经过多个关键阶段,包括纳米片堆栈图形化、浅沟槽隔离(STI)形成和栅极图形化。该架构的一个重要进展是在形成中间层和高k介电层之后实现垂直偶极图形化,使同一晶圆上的NMOS和PMOS器件能够独立调节阈值电压。

图3呈现了mCFET工艺架构的横截面透射电子显微镜(TEM)图像,显示了48纳米栅极间距和关键前端工艺组件,以及垂直图形化栅极堆栈的能谱分析映射。

2

先进互连架构

CFET设计包含了一系列复杂的互连特征,使其区别于传统CMOS技术。

图4显示了mCFET互连架构的TEM横截面图像,突出展示了正面和背面工艺特征,包括垂直金属化漏极局部互连(vMDLI)、金属化漏极(MD)、通孔(VD)、背面金属化漏极(BMD)、背面通孔(BVD)和背面栅极通孔(BVG)的实现。

该架构的一项关键创新是垂直金属化漏极局部互连(vMDLI),在顶部n型外延层和底部p型外延层之间建立直接连接。背面触点和互连的集成(包括BMD、BVD和BVG)提供了更大的设计灵活性和更高的布线效率。

图5展示了在不同VDD水平下(最高达1.2伏特)测得的mCFET反相器电压传输特性。

3

电学性能与特性

CFET反相器的电学特性展现出出色的性能。

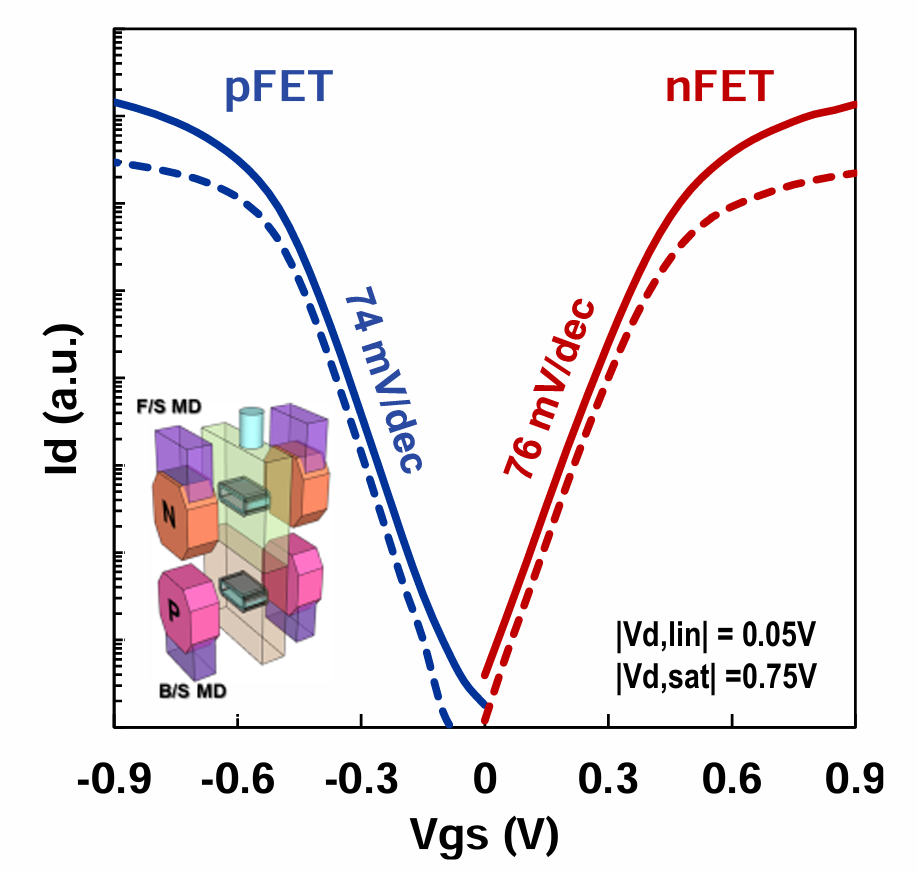

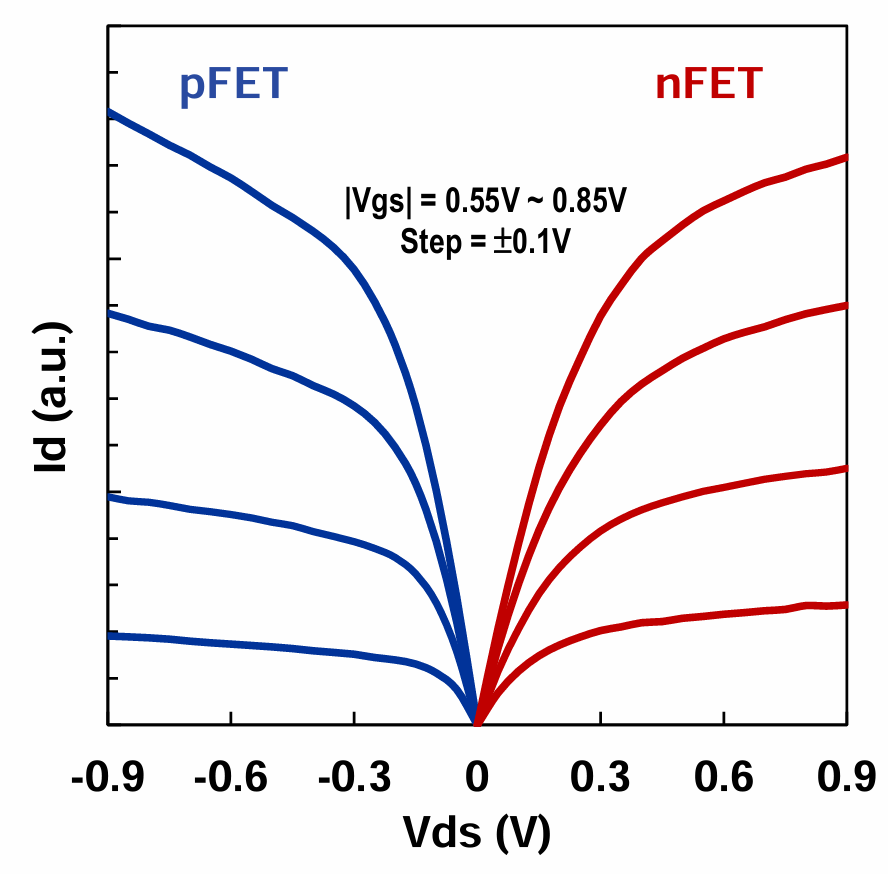

图6显示了具有正面源漏极接触的顶部nFET和具有背面源漏极接触的底部pFET的Id-Vg和Id-Vd特性,展示了优异的性能指标。

实现的器件展现出优异的亚阈值摆幅(SSsat):nFET为76 mV/dec,pFET为74 mV/dec,以及漏极诱导势垒降低(DIBL)值:nFET为54 mV/V,pFET为47 mV/V。这些指标验证了制造工艺和架构设计的有效性。

4

先进特征与性能对比

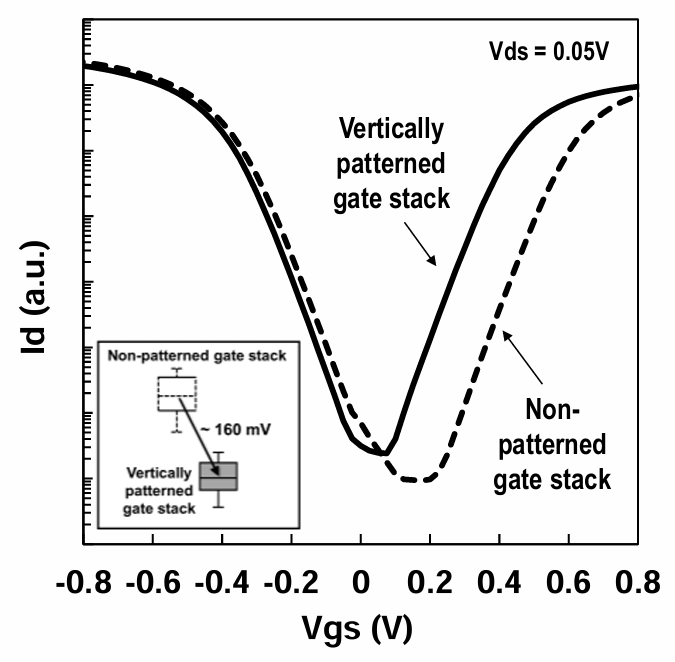

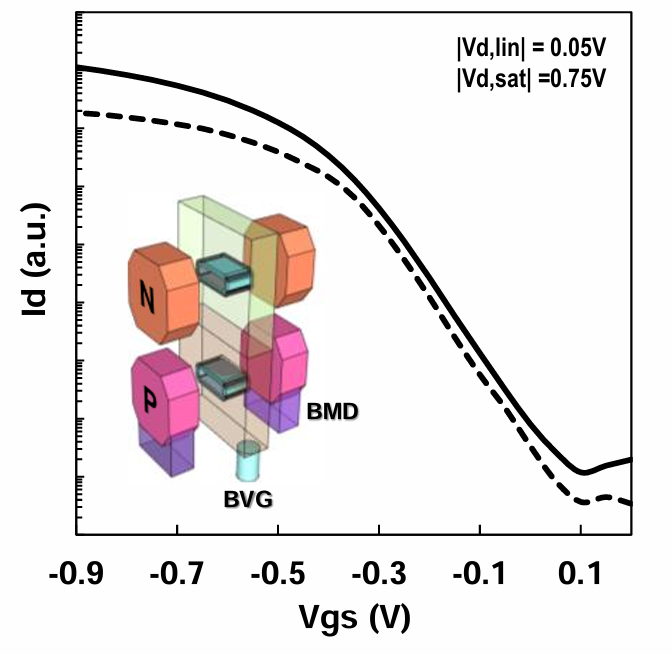

图7展示了各种电学特性,包括vMDLI实现、阈值电压调节效果和背面栅极接触性能。

这项CFET技术的成功实现,结合已展示的电学特性,标志着半导体器件架构的重要进展。在48纳米栅极间距下实现完全功能的反相器,为逻辑技术发展提供了新的参考。

暂无评论