凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片一个设置改动,噪底飙升27dB,我还找不着原因

(1)

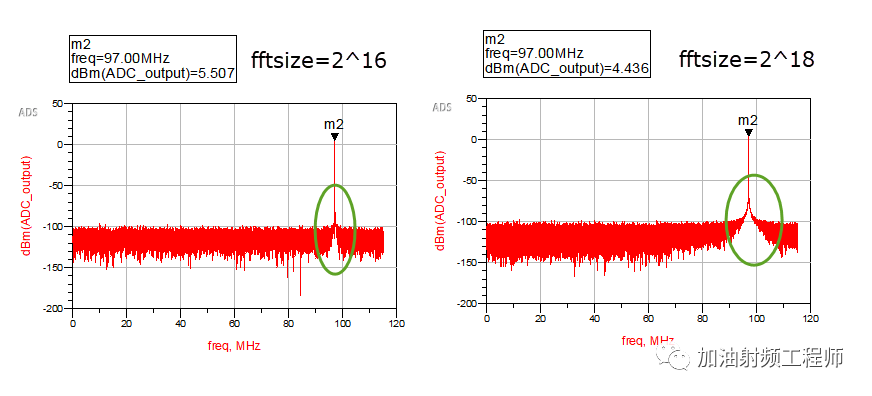

问题的起因,是因为我更改了一下FFTSIZE的设置。

原来,我设置的是16,也就是打算让ADC采样2^16=65536个点的。

但是,在排查其他问题的时候,我把FFTSIZE改成18了。

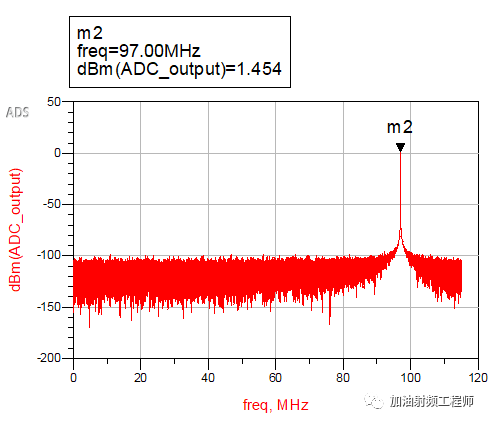

然后,就出现了下面这种情况,也就是信号那边抬上来了。

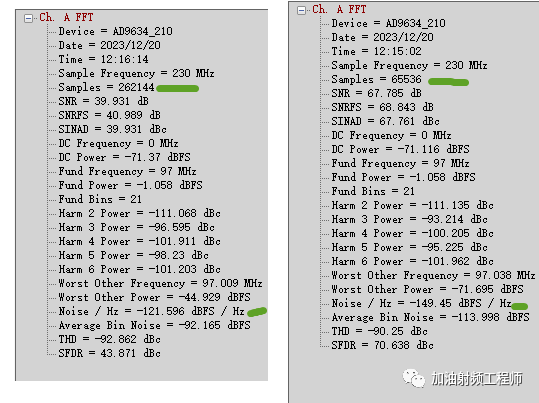

要是把code的数据,导入到VisualAnalog,看ADC的噪底的时候,发现噪底瞬间抬高27dB左右。

(2)

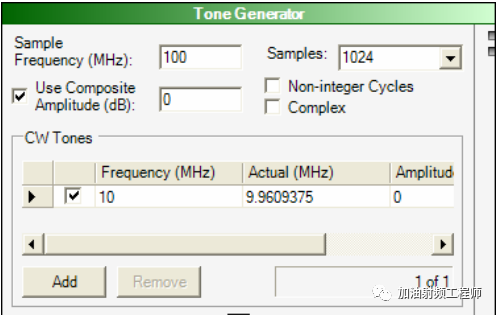

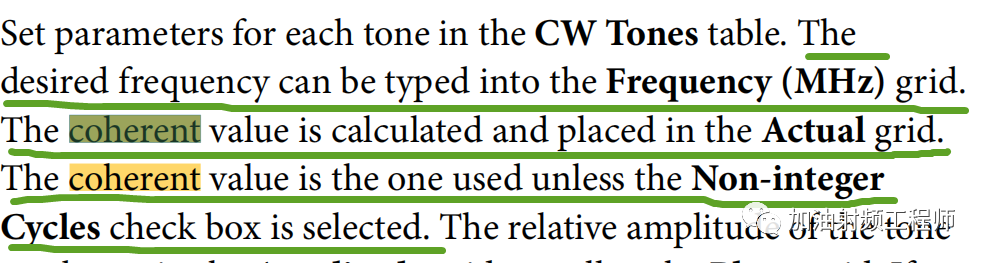

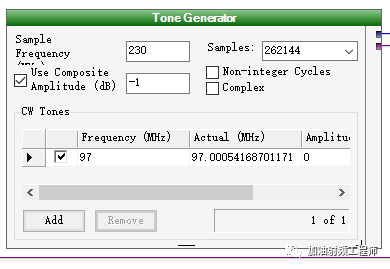

ADI的VisualAnalog上,进行输入信号设置的时候,在Frequency旁边有一个Actual值,如下图所示。

看help文件,有这样一段话。

意思就是,Actual(MHz)下方的频率,才是实际的源的频率。这边有涉及到coherent sampling的概念。

(3)

那ADS里面,仿真出现这个问题,会是这个原因么?

于是,我在VisualAnalog中设置了一下,算出一个Actual频率,并且把它代入ADS中。

但是,仿真出来的结果,并没有什么改变,仍然是抬高的。

所以不是这个原因造成的。

然后在ADS里面不断的更改设置,发现越改越茫然,发现仿真结果越来越不可控。

我好想变成一只鸵鸟,假装这一切都没有发生,我没有把FFTSIZE设置成2^18。

(4)

同时,又发现ADS里的AtoD的ADC模型,并不是不能在欠采样的情况下,折叠到第一奈奎斯特域,而是它对输入源有要求。

如果用Sinusoid作为输入,就能;如果用N_tone作为输入,就不能。

哎,把我整不会了。很惆怅~

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论