凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片 一文简谈:CPU内部晶体管是如何工作?!

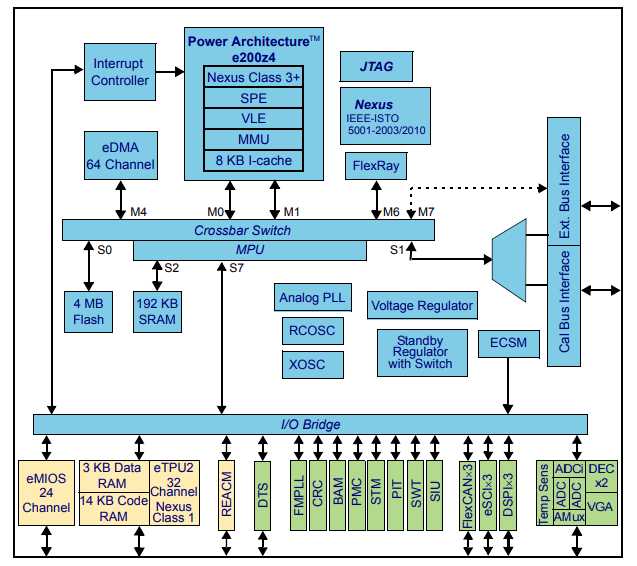

你知道吗,在0.1平方厘米的硅片上,数十亿个晶体管以光速开合,构成了现代CPU的计算引擎。这些微观电子开关如何实现加减乘除?又如何驱动3A游戏与AI推理?下面将谈谈这些!

1、晶体管:CPU的数字开关

MOSFET结构解析

三极结构:栅极(Gate)、源极(Source)、漏极(Drain)构成电流通道。

工作原理:栅极电压控制沟道导电性,实现电流通断(类似水闸)。

CMOS逻辑基础

NMOS与PMOS对管组合:NMOS导通低电平,PMOS导通高电平。

逻辑门实现:非门仅需1个NMOS+1个PMOS,与非门需2对CMOS管。

2、晶体管阵列:从门电路到运算单元

加法器结构

全加器核心:异或门(XOR)计算本位和,与门(AND)生成进位。

晶体管数量:1位全加器需28个晶体管(静态CMOS实现)。

乘法器拓扑

Booth编码阵列:部分积生成需N×N晶体管矩阵(N为操作数位数)。

墙树型加法器:压缩部分积时使用4:2压缩器,每个单元含18个晶体管。

3、微架构级协同:晶体管群的舞蹈

时钟同步机制

主频决定开关速度:5GHz CPU每纳秒完成1次开关周期。

时钟树分布:H型拓扑确保时序偏差<10ps(需缓冲器级联)。

电源门控技术

睡眠模式:通过Power Gating晶体管阵列切断闲置模块供电。

唤醒延迟:门控管开启需数百纳秒,需预判任务调度时机。

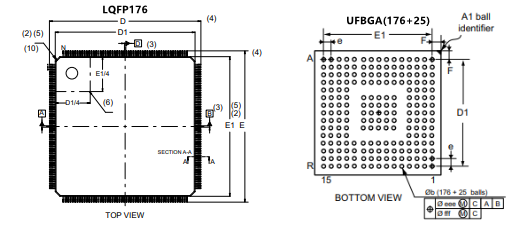

4、制造工艺的进化论

①FinFET革命

三维栅极结构:Intel 22nm工艺实现电流控制能力提升37%。

鳍片间距:台积电5nm工艺鳍片间距缩至28nm(仅为病毒直径的1/3)。

②GAAFET前瞻

纳米片堆叠:三星3nm工艺采用4层水平纳米片,驱动电流提升30%。

接触电阻:GAAFET接触电阻降至6Ω·μm(FinFET为12Ω·μm)。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论