凡亿教育-雯雯

凡事用心,一起进步打开APP

公司名片ARM JTAG调试架构解析:组件与底层逻辑

JTAG是ARM芯片调试的核心接口,其架构通过分层设计实现主机到芯片的指令透传。下面将聚焦ARM JTAG调试架构,理清楚其物理层和协议层关键组件。

1、ARM JTAG调试结构的三大模块

①Debug主控(Host)

功能:运行调试软件的PC端,发送高级指令(如断点、内存读写)。

工具:ARM SDT/ADS套件中的ADW(Windows)或arm-elf-gdb(Linux)。

②协议转换器(Protocol Converter)

核心作用:将主机的高级指令转换为JTAG扫描链可识别的底层信号。

通信介质:支持USB、以太网、RS-232等物理接口。

协议标准:

主流采用ARM Angel协议(参考SDT/ADS文档)。

第三方方案(如Abatron BDI、EPI Jeeni)可能使用私有协议。

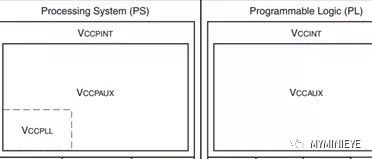

③JTAG宏单元(Macrocell)

硬件实现:集成于ARM7TDMI等内核中,包含:

3条扫描链(ScanChain):分别处理指令寄存器、数据寄存器、旁路信号。

TAP状态机:控制JTAG时序(如Shift-IR、Shift-DR状态切换)。

2、工作原理

主机通过调试软件发送指令(如“单步执行”)。

协议转换器将指令拆解为JTAG扫描链可识别的位流。

TAP状态机驱动扫描链,完成指令注入或数据回传。

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论