凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片石英晶振封装全解析:DIP VS SMD

对电子工程师来说,石英晶振的封装选择,是速度、成本u可靠性的三重博弈,如何根据项目需求及实际情况,合理选择其封装方式?

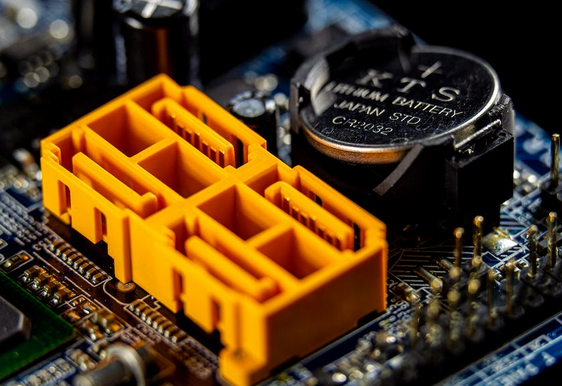

1、DIP封装

外观:双列直插式,引脚分立两侧,形似“蜈蚣脚”。

引脚数:4~6脚为主流,部分测试型号带TEST引脚。

关键引脚:

VCC:接电源(3.3V/5V),接反即“冒烟”。

GND:地线,必须与PCB地平面直连。

OUT:输出时钟信号,需匹配负载电容(通常18pF)。

OE:使能控制,高电平禁用输出(部分型号无此脚)。

2、SMD封装

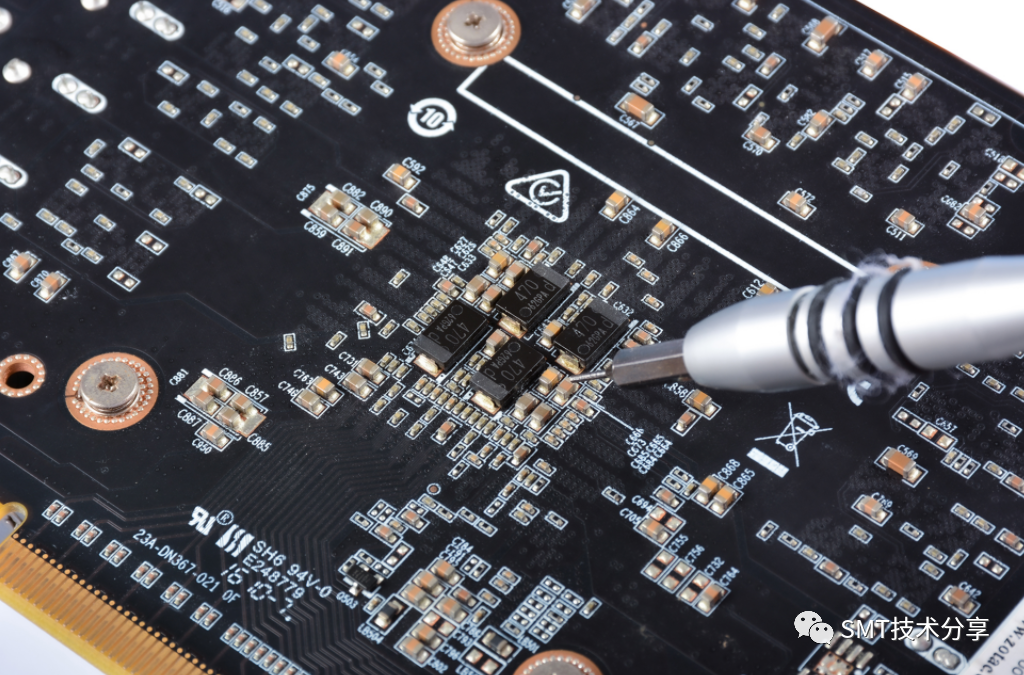

外观:底部贴片式,引脚密集如“蚂蚁腿”。

引脚数:4~8脚常见,小型化封装(如2016/3225)更紧凑。

关键引脚:

VCC/GND:同DIP封装,但焊接不良易导致频偏。

OUT:输出端,需远离干扰源(如大电流线路)。

OE:悬空可能引发信号异常,必须按Datasheet处理。

FB:反馈引脚,接振荡电路形成闭环(部分型号集成)。

3、封装对比:选型不踩坑

本文凡亿教育原创文章,转载请注明来源!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论