判断一个信号是否为高速信号首先要区分几个误区。

误区一:信号周期频率FCLOCK高的才属于高速电路设计

其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。

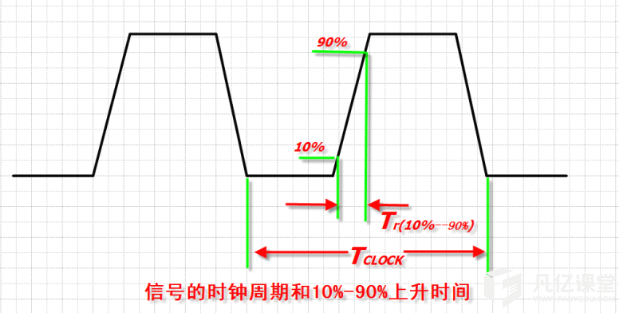

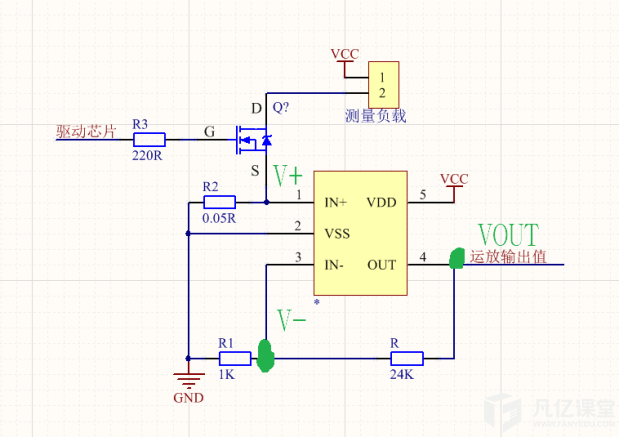

如上图信号周期频率与有效(转折)频率定义为:

(实际中多数信号)

误区二:电容、电感式理想器件

在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C两侧表现出的电抗值为1/2πF×C,在工作频率很高的情况下电抗值变得很小,电容表现为短路。

认清上面两个误区我们来讨论低速信号和高速信号的问题。对于低速信号而言,传输路径上的个点的电平近似相同,我们可以采用集总的思维来对待传输路径,即传输路径上的各点状态相同;对于高速信号而言,传输路径上的各点电平不同,需要采用分布式的思维来看待,即各个点的状态不同。因此,高速低速区分还要看信号传输路径的长度。

一般而言,在信号传输路径的长度(即信号线的长度)小于信号的有效波长的1/6时,可以认为在该传输路径上,各点的电平状态近似相同。由信号波长与频率的关系我们可以按下面的步骤进行高速低速的区分;

1、获得信号的有效频率Fknee和走线长度L

2、利用Fknee计算出信号的有效波长λknee

3、判断L与1/6λknee的关系,若L>1/6λknee,则信号为高速信号;反之,则为低速号。

注意:Fknee的获得方式一是可以直接测量,二是经验值可以假设信号的上升沿时间为信号周期的7%,此时有效频率Fknee约为周期频率FCLOCK的7倍,如周期频率FCLOCK100MHz的时钟信号,可以估计其有效频率约为700MHz。

综上,我们还可以得到传输线和非传输线的概念。和高速低速信号的判断一样,高速号的走线我们视为传输线,反之亦反。

我们来看个例子。

判断下面走线是否为传输线?

信号1:FCLOCK为100MHz,上升沿时间2ns,走线长度L为6in(英寸);

信号2:FCLOCK为100MHz,上升沿时间0.5ns,走线长度L为6in(英寸)。

对于信号1:

Fknee=0.5/2ns=250MHz

λknee=C/Fknee=(3×108m/s)/250MHz=1.2m=47in

对于信号1:

Fknee=0.5/0.5ns=1000MHz

λknee=C/Fknee=(3×108m/s)/1000MHz=0.3m=12in

其中:1m=39.37in。

信号1的走线长为6in,小于λknee的1/6,因此可以视为非传输线;

信号2的走线长为6in,大于λknee的1/6,因此应视为传输线。

暂无评论