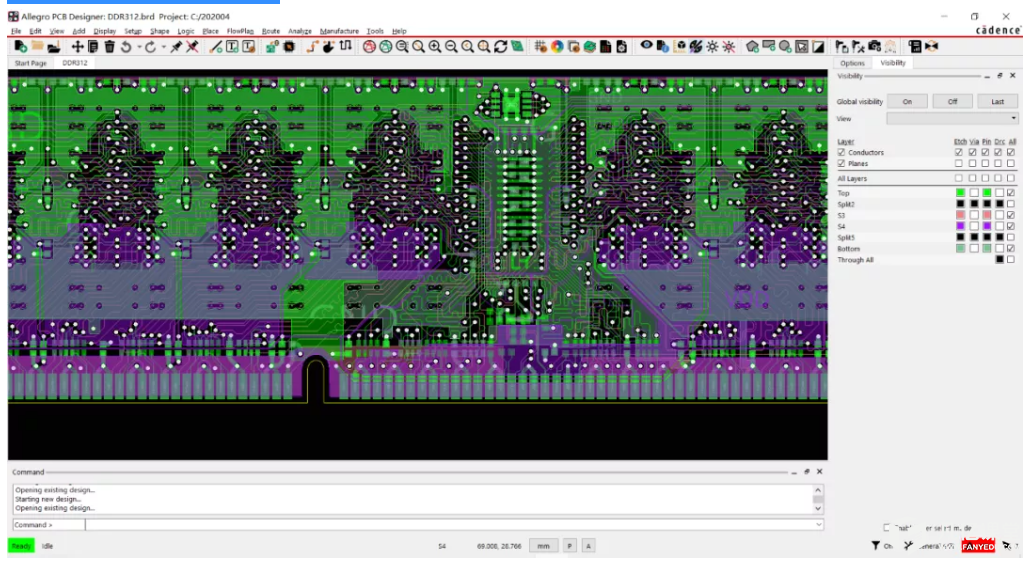

A

llegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

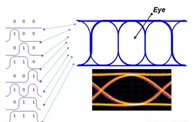

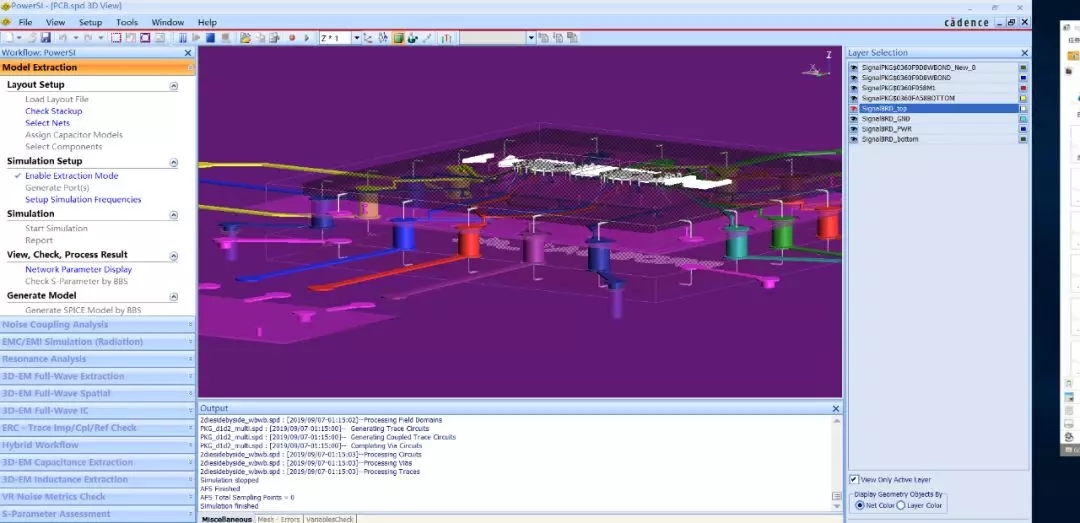

今天我们一起来学习使用Allegro软件进行DDR3_DIMM2RX8内存条实例文件的仿真分析方法,以及对内存条的信号进行互连提取并进行高速信号眼图分析和验证的方法。

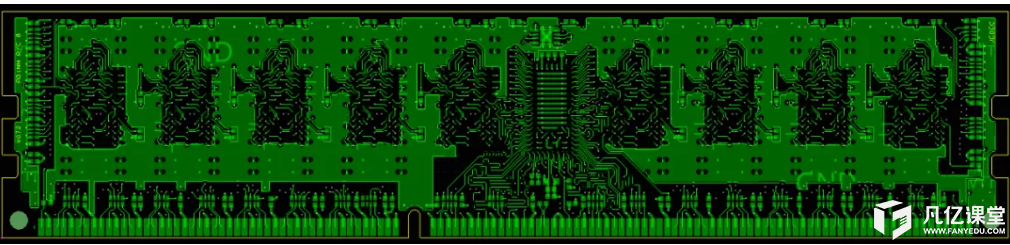

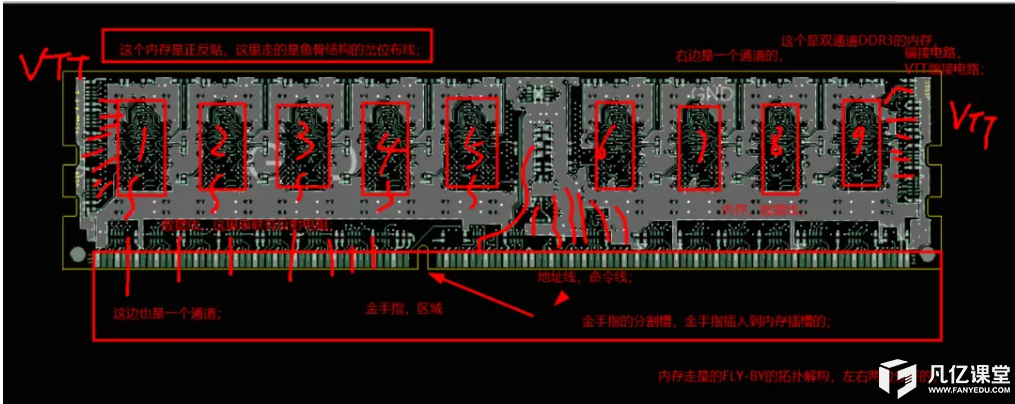

【1】打开文件进行解读文件,深入了解文件中对各个信号的分配情况以及对内存芯片、VTT端接、金手指的位输入、内存的控制等。

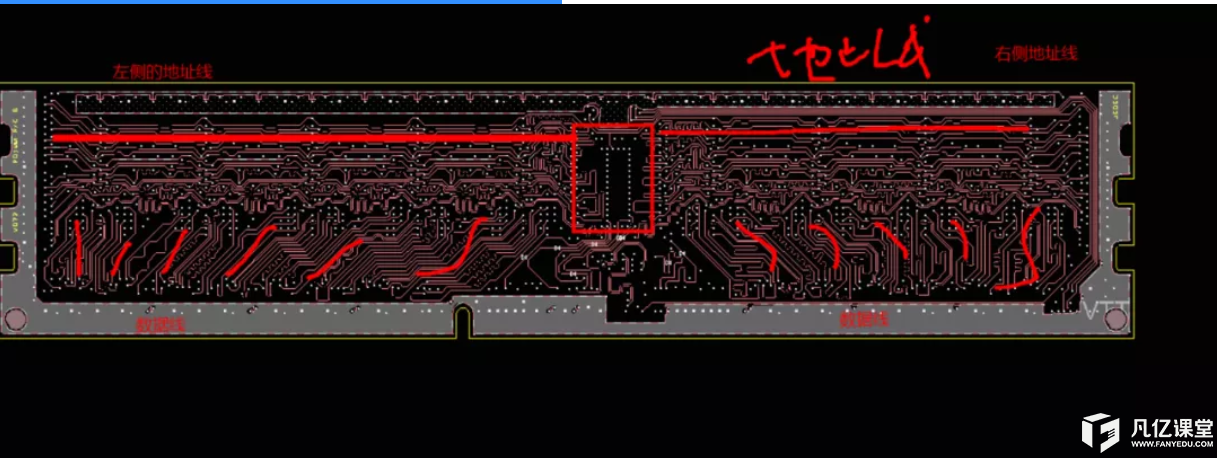

【2】下图文件中TOP层已经标出了内存文件中各个内存的关键元件和关键信号的位置,内存的芯片采用FLY-BY的信号拓扑结构,数据信号中有串联信号反射电阻。

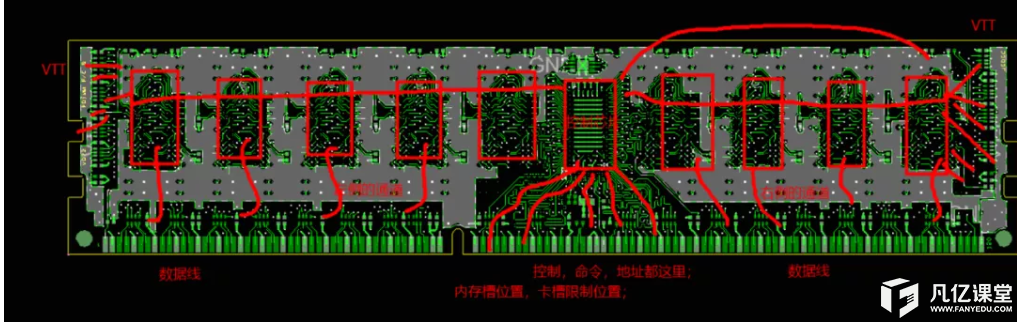

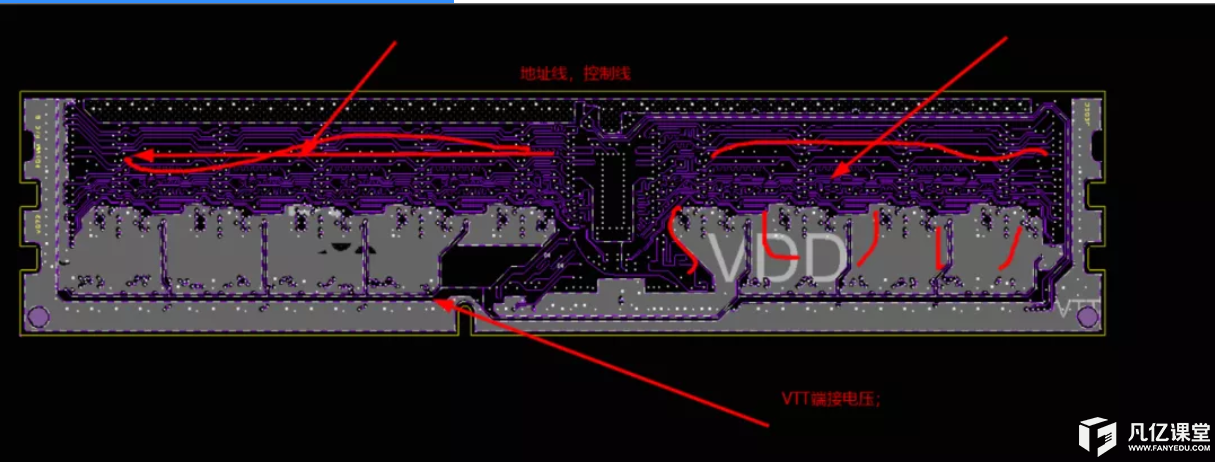

【3】下图为实例文件的BOTTOM层,图中给出了内存颗粒的位置及数据组信号的位置、和内存控制芯片的位置、VTT的信号端接的位置。从下图可以看到关键元件的布局和分布情况。

【4】下图为内层的S3层,可以看到靠近上面都是内存芯片的地址线,下面的是内存的数据线。右侧的地址线,右侧的内存复用连结。左侧的地址线,左侧的内存复用连结,两侧通道地址分开各自有自己独立的VTT端接电路。

【5】下图是内层的S4层,可以看到靠近上面都是内存的芯片的地址线,下面VREF参考电压网络及VDD的1.5V网络电源平面。

【6】第2层和5层都是电源和GND的参考层,为高速信号提供稳定的电压和信号回流。

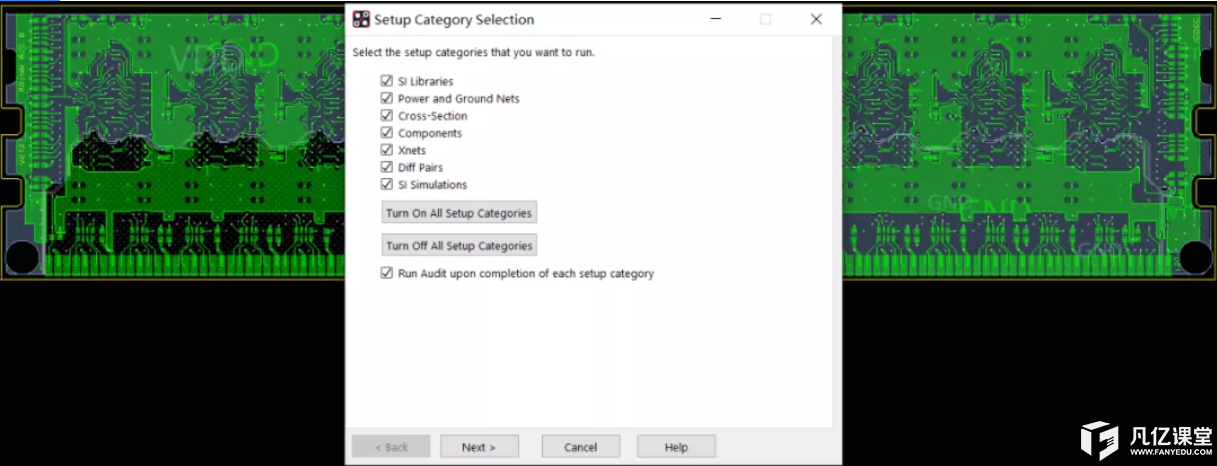

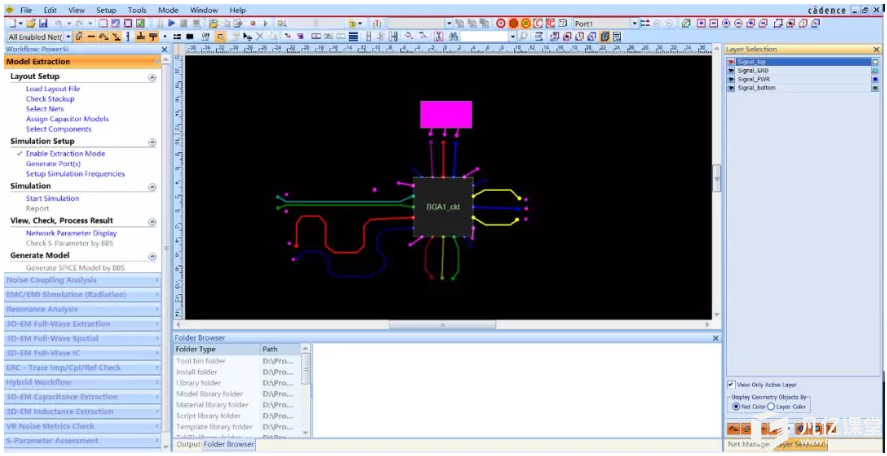

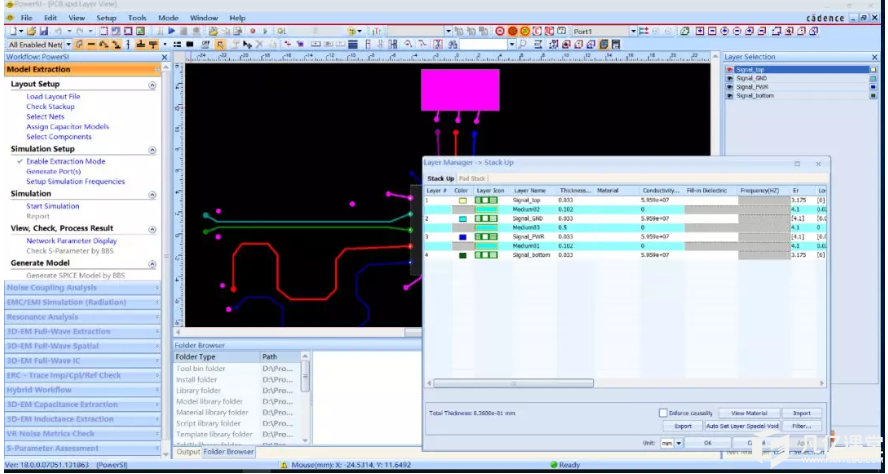

【1】在Setup Category Selection窗口中,用来选择进行执行信号完整性仿真的必要设置,比如进行库的设置、电源的归类设置、层叠设置、元件类型设置、网络设置、差分对设置等。

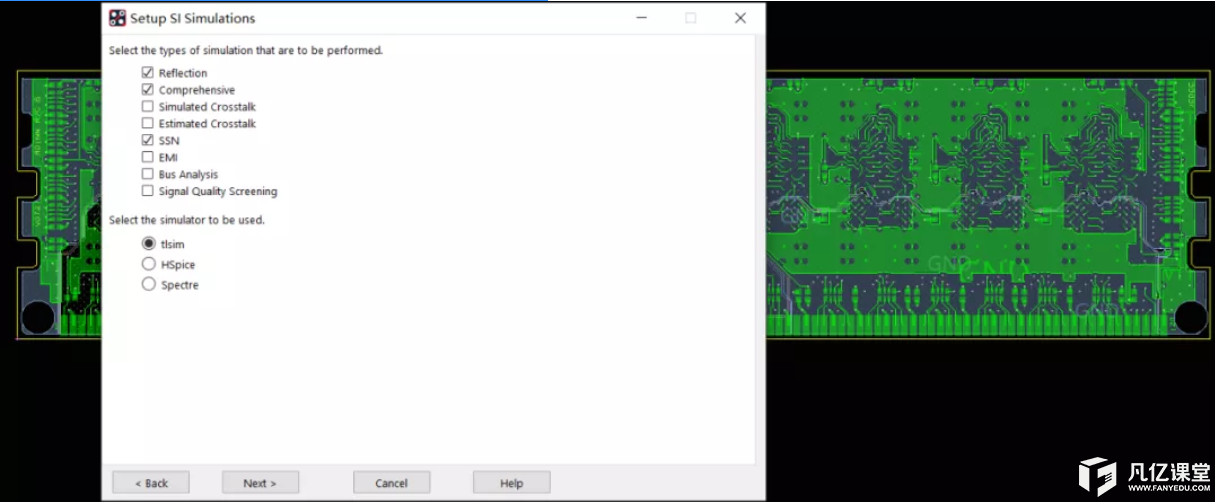

【2】选择Next之后可以进入XNET网络的设置、模型库的路径设置、模型库支持类型的设置、DML和IML文件的工作路径、电源和GND网络的归类设置、层叠的设置、元件的类型设置、差分对网络选择和设置等。选择Next之后所需要进行设置的项目均已经配置完成,接下来,在弹出的窗口中可以选择需要执行信号完整性仿真的类型及仿真器的选择。常用的Refection可以执行信号反射的仿真分析。

Cadence Allegro 软件也支持手动进行库的设置、电源的归类设置、层叠设置、元件类型设置、网络设置、差分对设置等,也能进行高速信号相关的仿真。比如:

【1】进行仿真库的设置;

【2】信号和电源的归类设置,

【3】电源要赋予电压,层叠的设置;

【4】原件模型设置,三种模型;

【5】XNET网络设置;

【6】差分对设置;

【7】检查仿真的网络相关设置是否正确等。

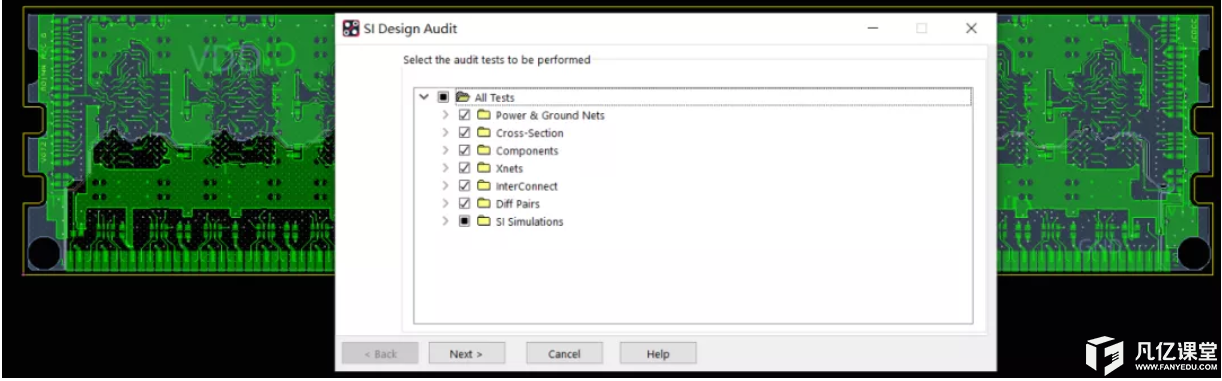

针对有设置存在错误的地方,软件有集成的SI Design Audit 高速信号仿真检查功能,可以对设置中存在的错误的地方进行稽核和修改。

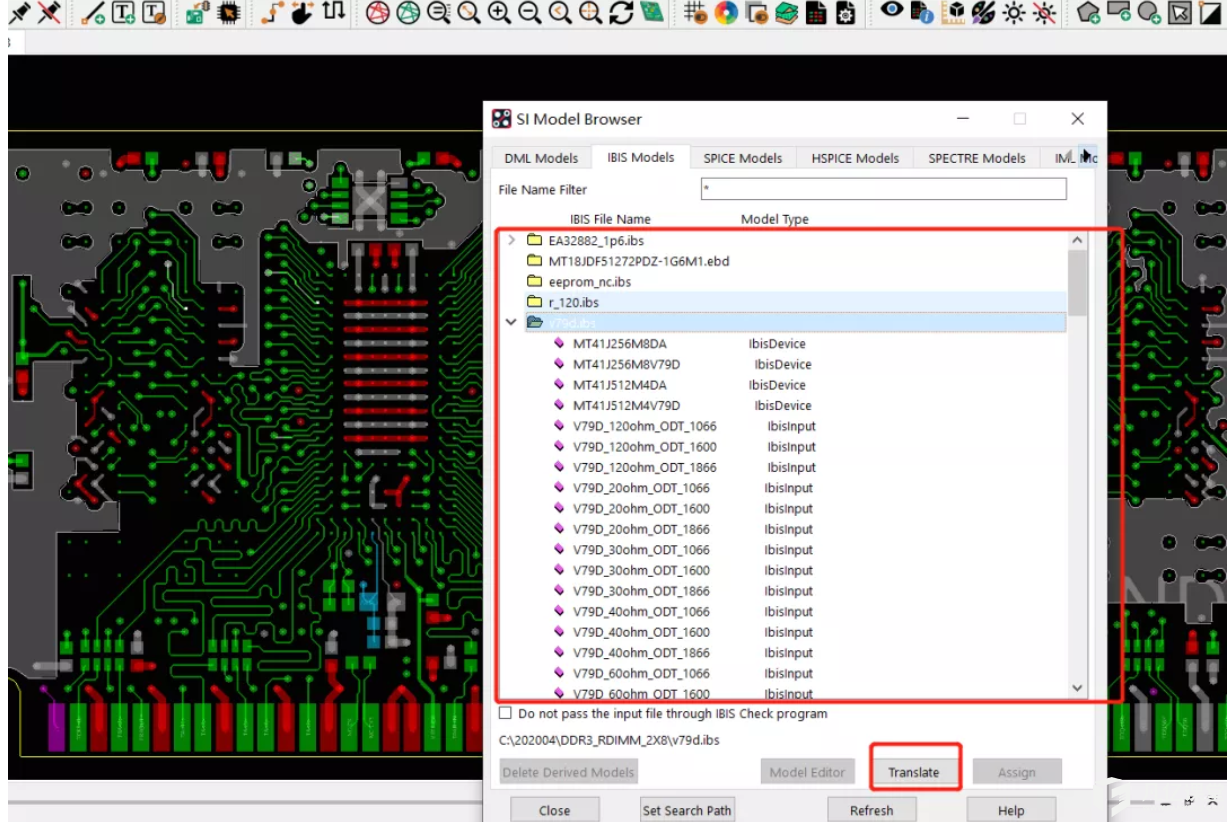

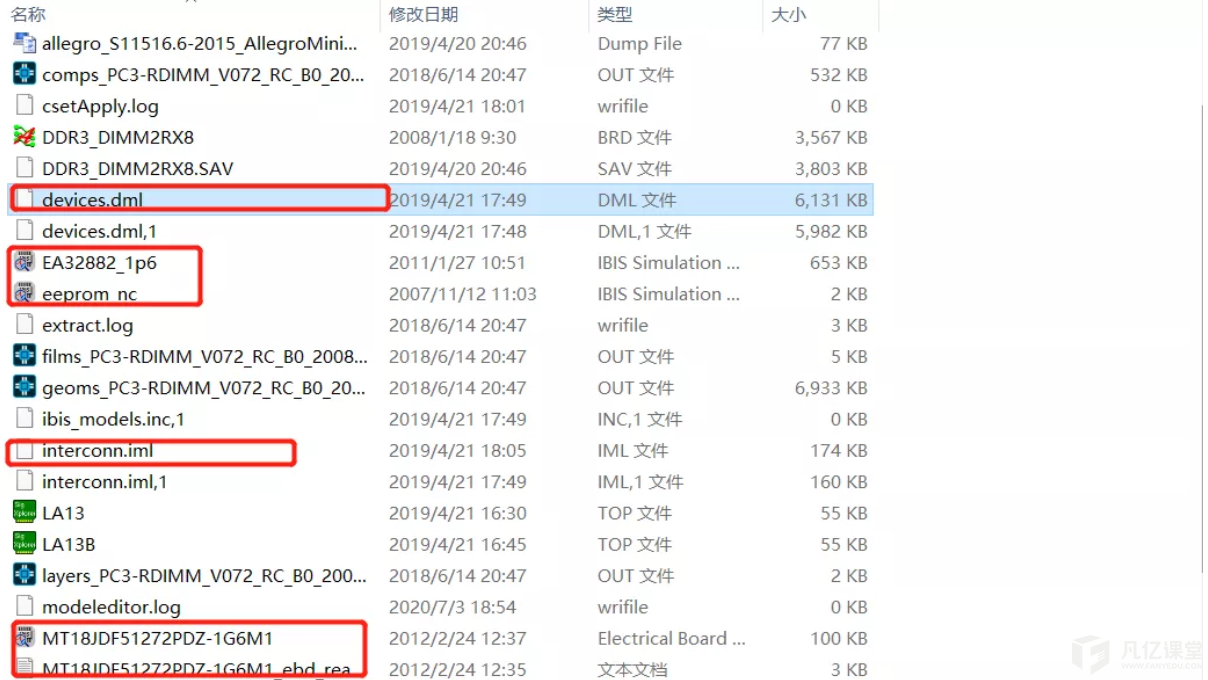

【1】在SI Model Bowser窗口中可以直接进行DML文件转换,选择需要进行转换的文件,点击Translate就可以完成DML的转换操作。

【2】相关的文件转换完成以后,在当前的工作路径下就可以看到,已经转换完成的文件。

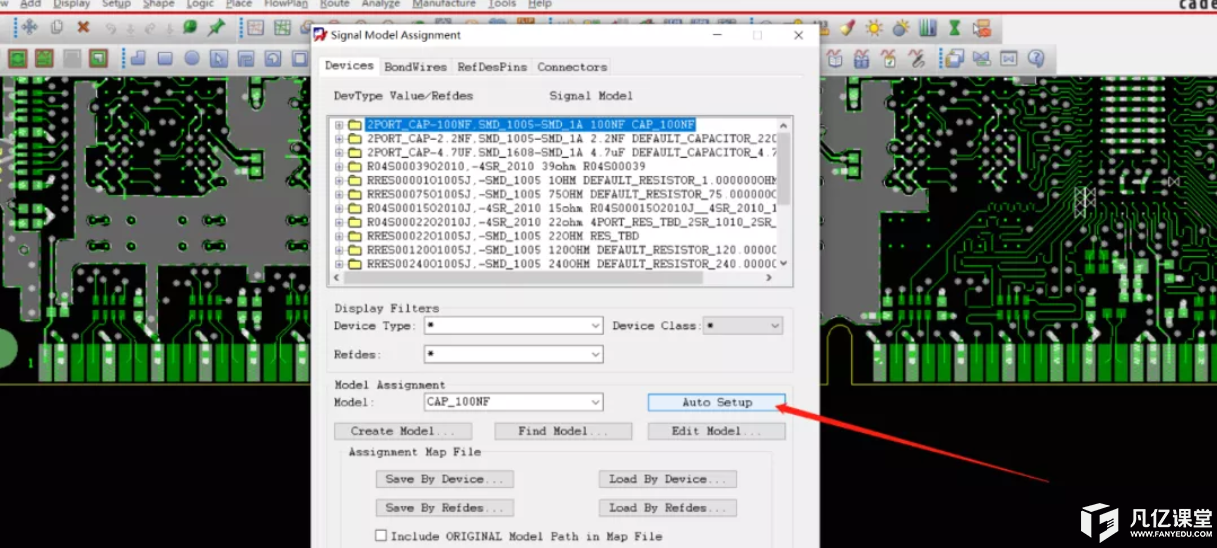

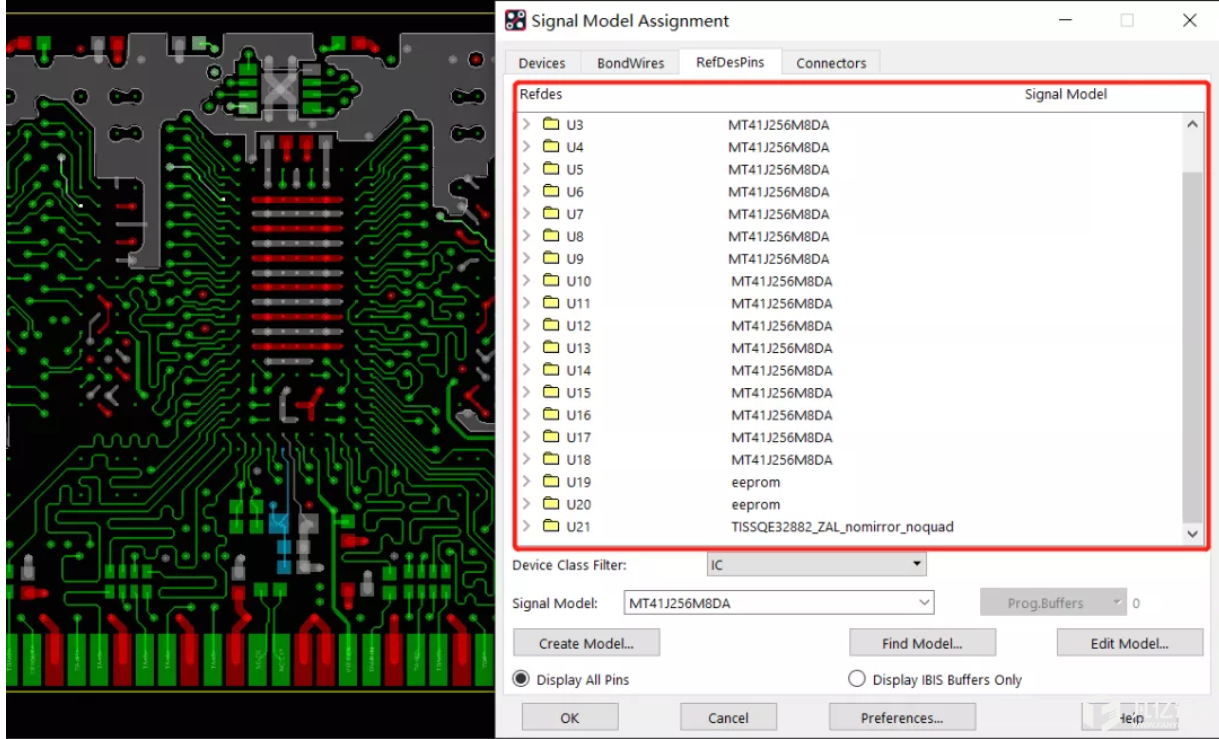

【3】在Signal Model Assignment窗口中对DDR3_DIMM2RX8文件中的各个元件的模型进行检查,看是否有模型存在错误或者漏做。

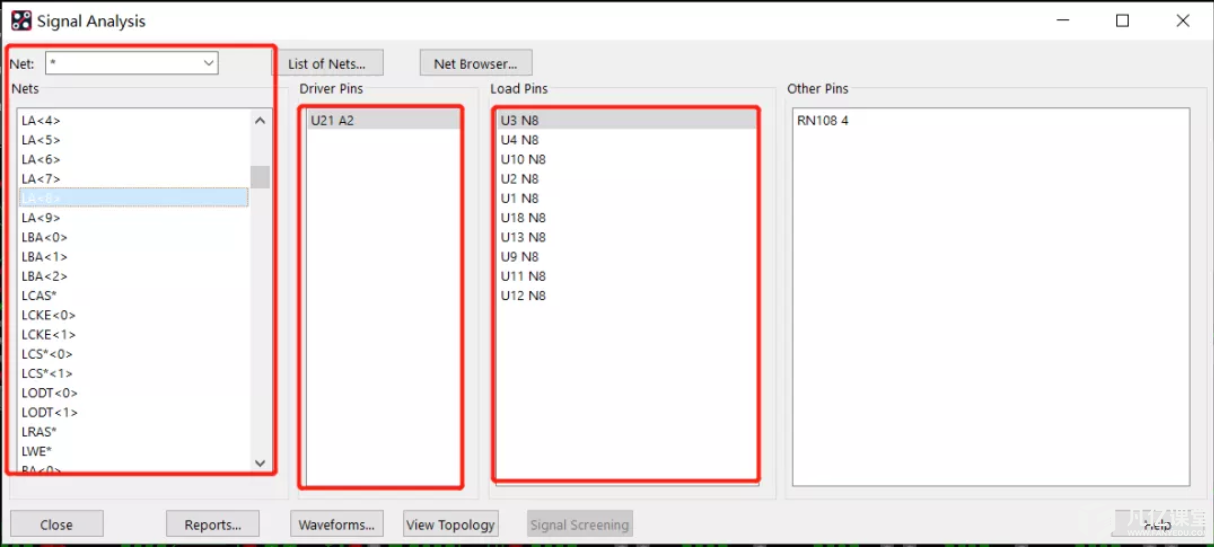

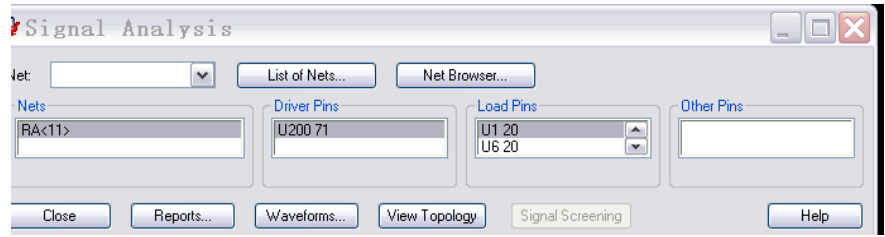

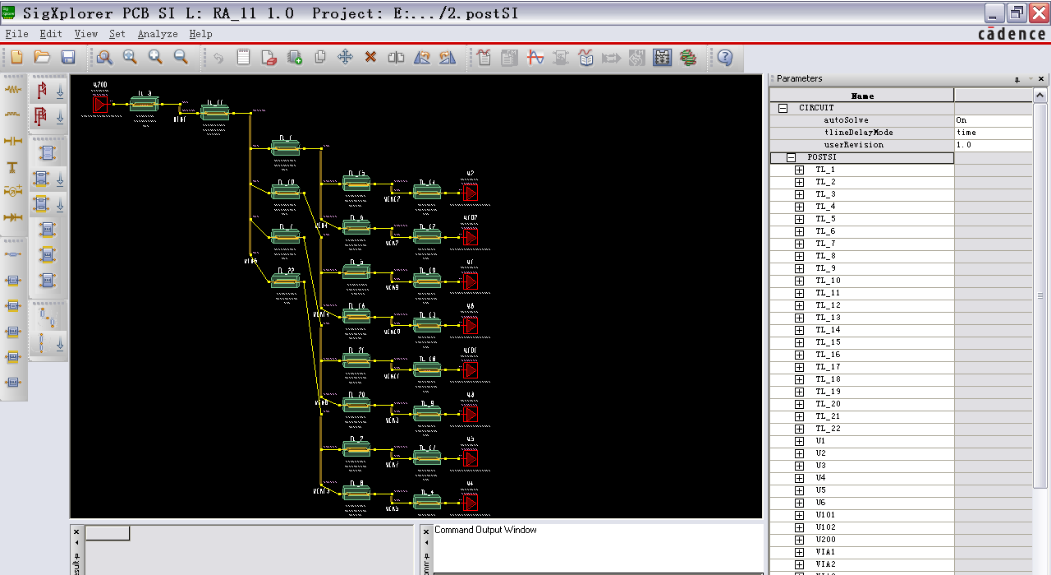

【1】在Signal Analysis窗口中提取信号仿真链路,需要提前将芯片的模型、原件的模型、IO的模型、连接器的模型等和信号链路有关系的模型都赋予完成,只有这样才能提取正确的拓扑互连模型。

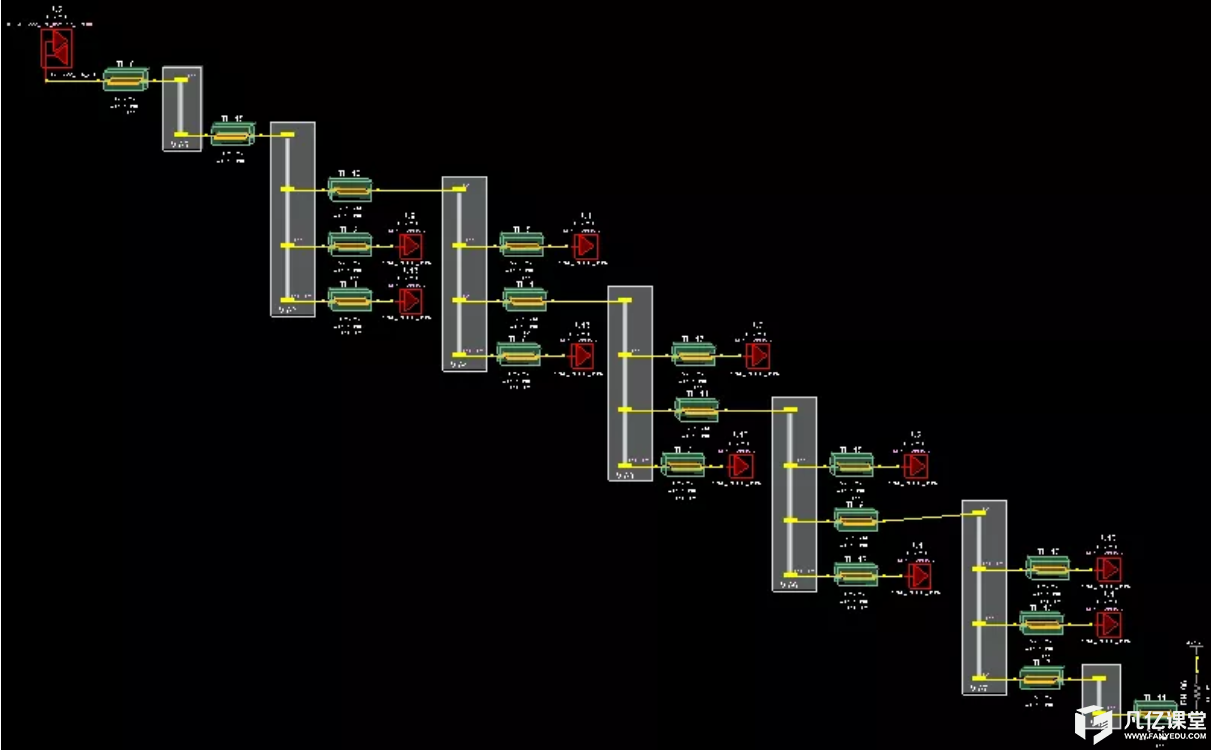

【2】点击View Topology按钮,开始提取LA

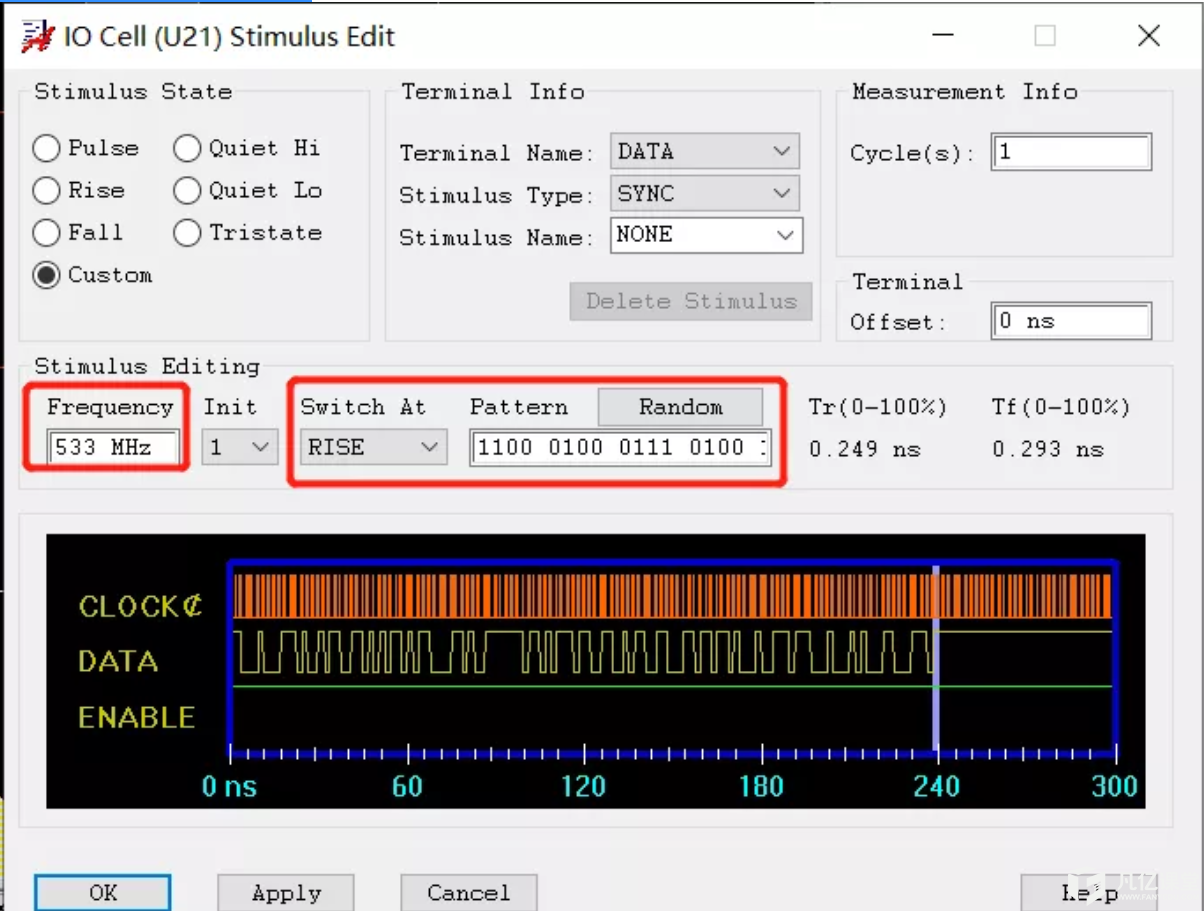

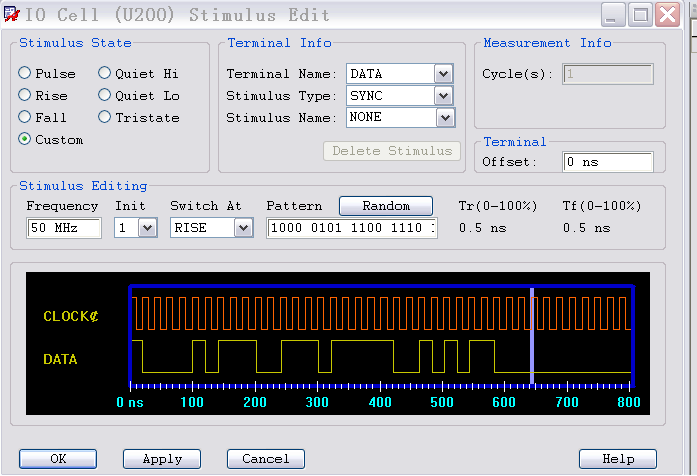

【3】在U21TISSQE32882芯片Cell模型上点击右键,设置信号的的激励模型,采用自定义的信号533MHz信号频率。

6仿真结果眼图分析解读&时钟线拓扑链路提取与拓扑整理

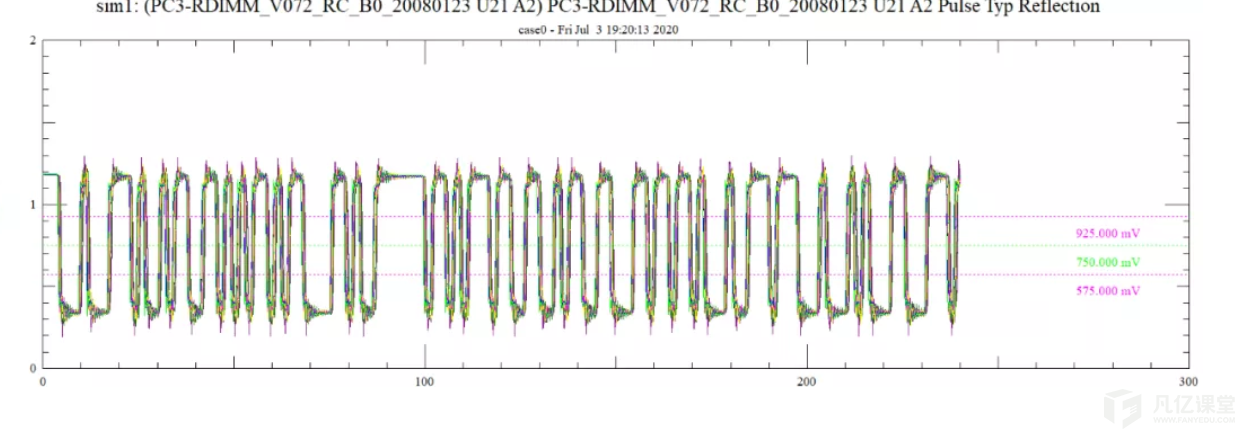

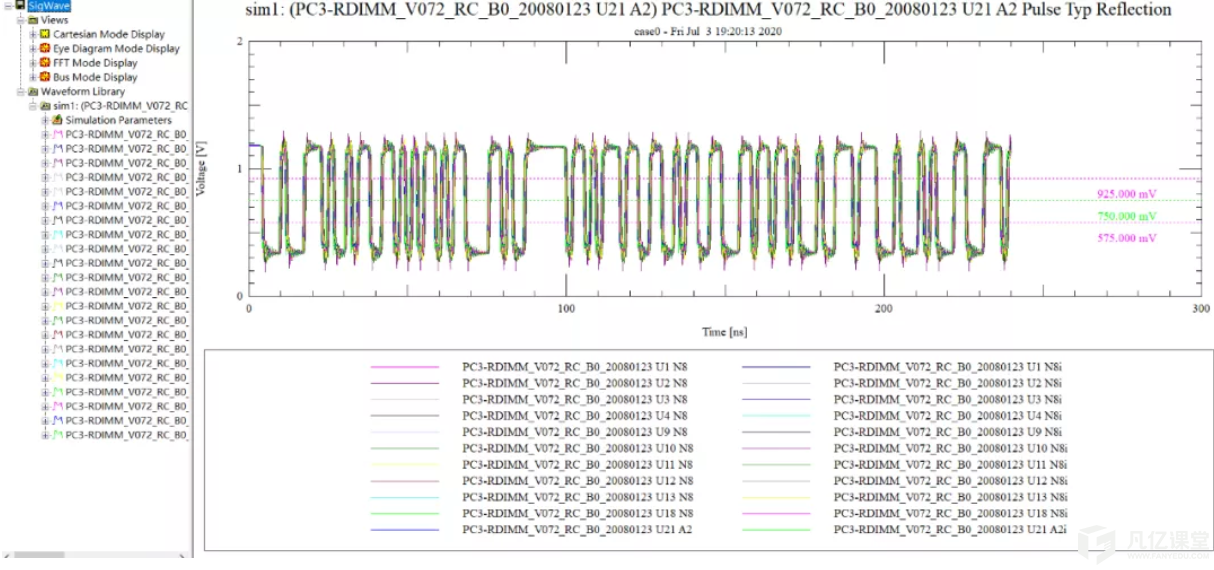

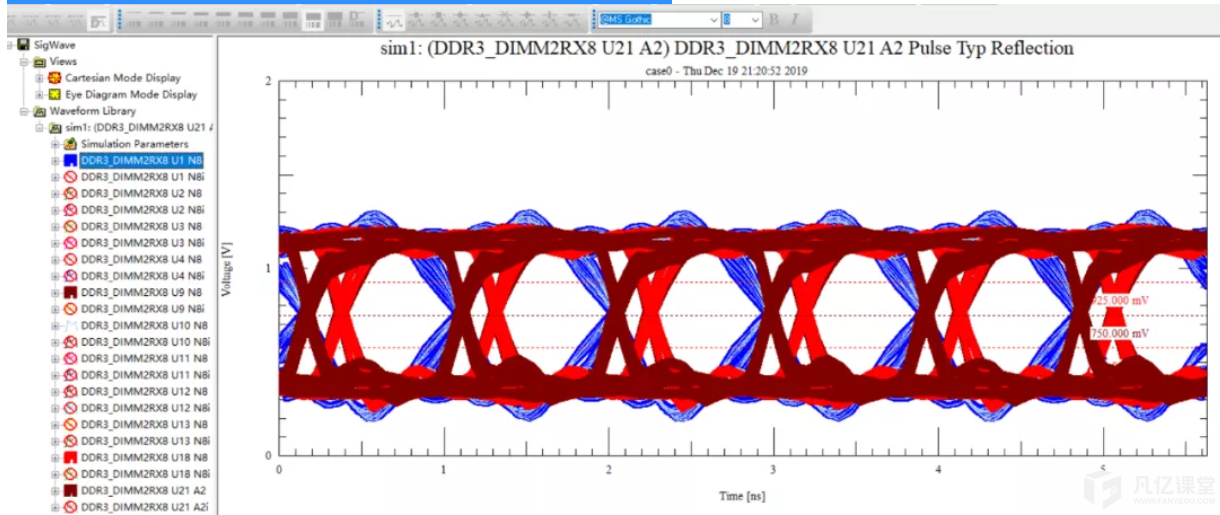

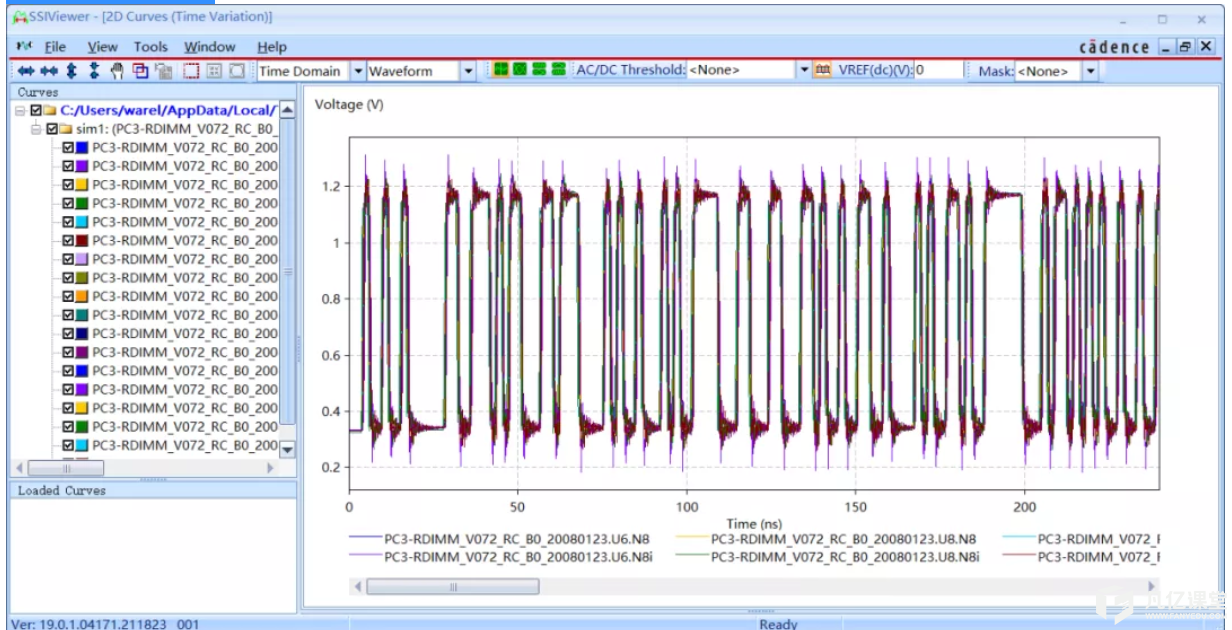

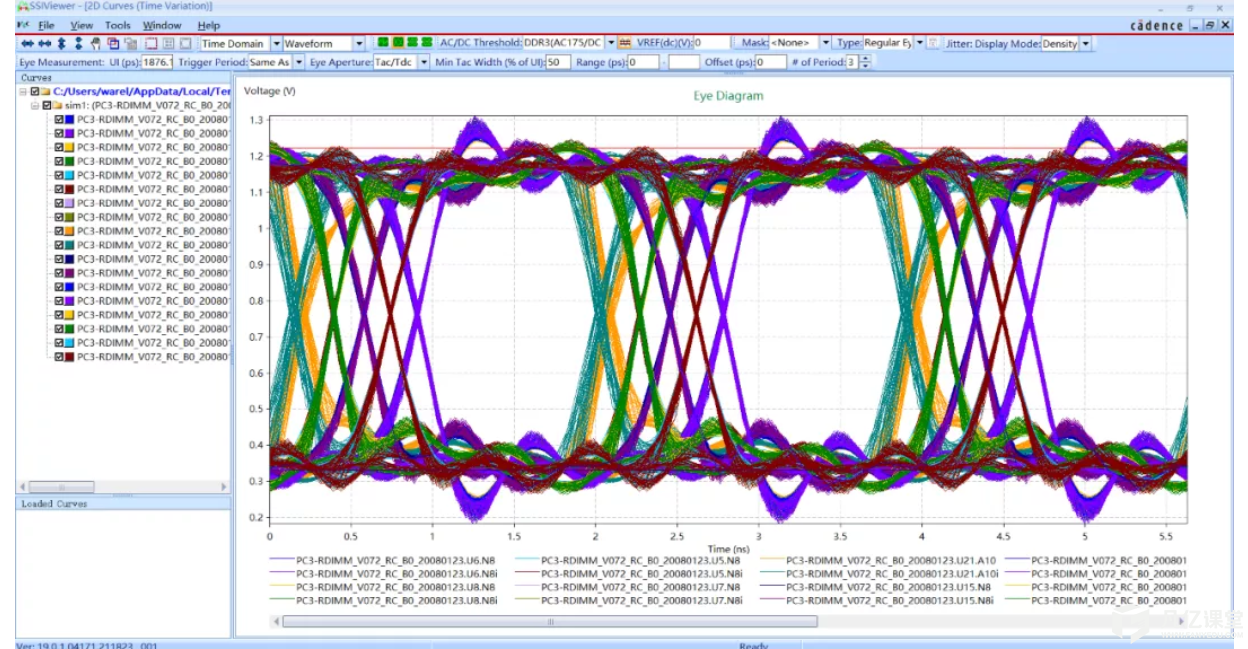

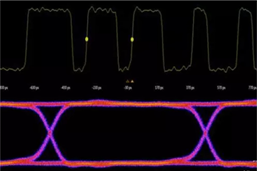

【1】执行仿真,完成后可以看到时域的仿真结果如下图所示。

【2】SigWave中显示出的就是执行完成的信号仿真信号,左侧给出了各个信号的名称,方便进行信号的区分和结果分析。

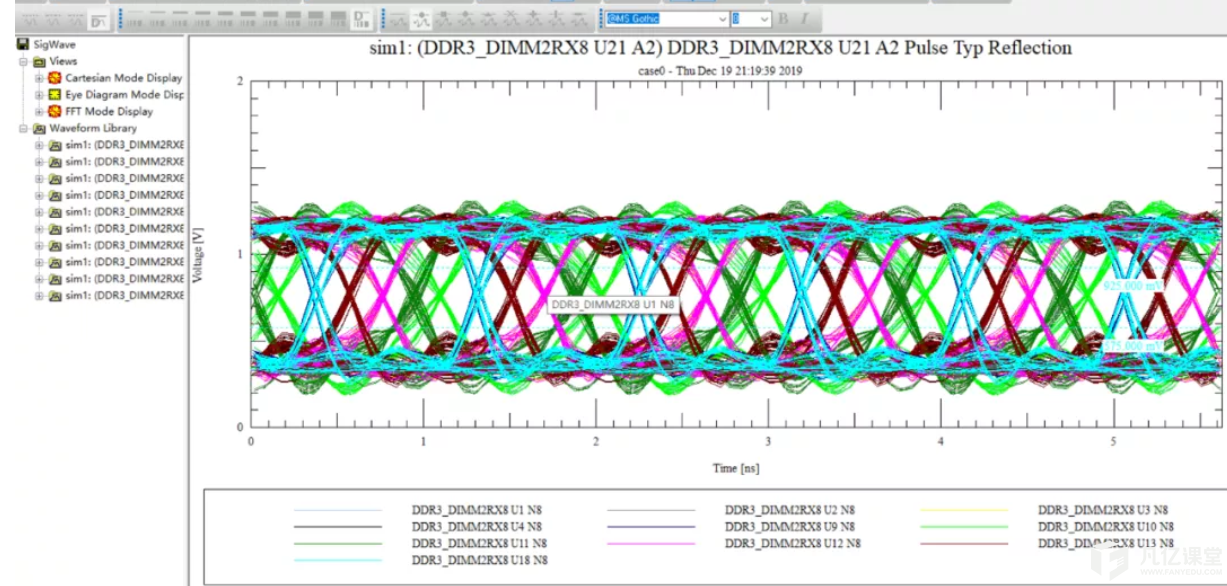

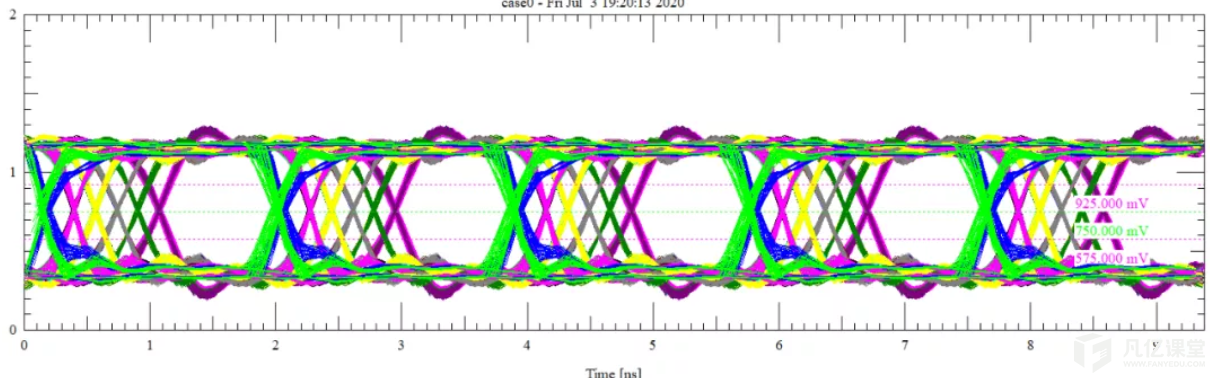

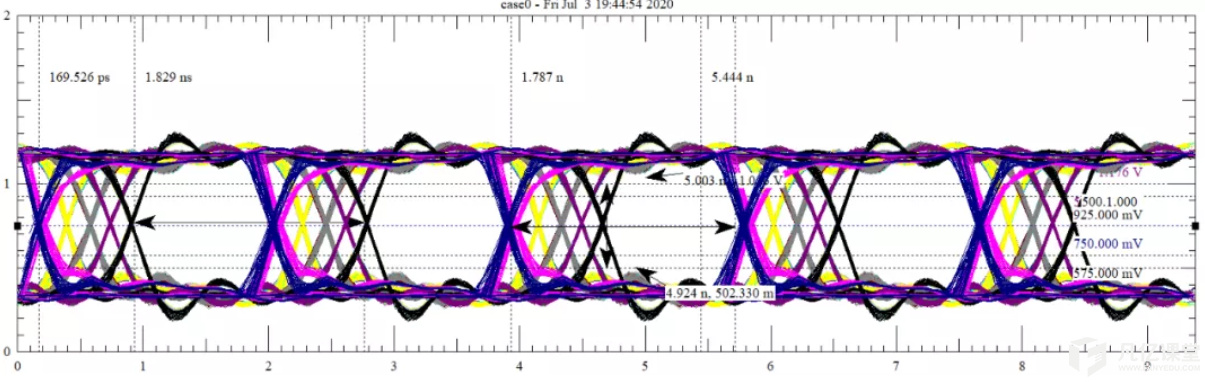

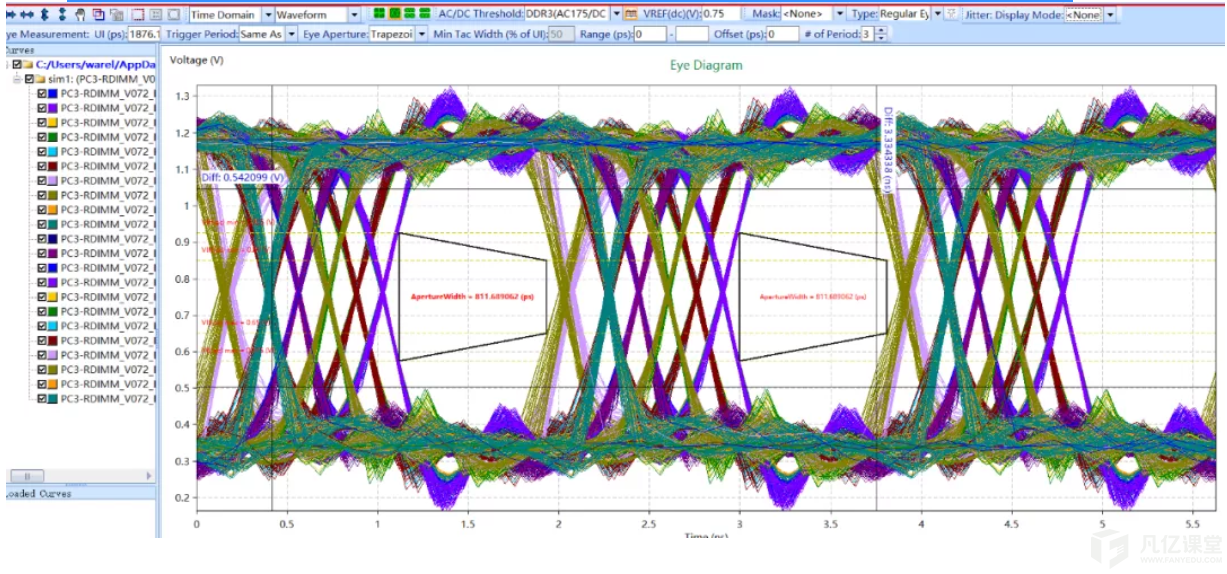

【3】点击眼图模型,设置模板参数为533MHz,设置眼图数量为5,对数据的结果进行整理。对地址线的数据线结果进行整理,对眼图的结果进行分析。

【4】找到地址线发送端口和接收端口,对信号进行整理。整理完成的信号如下图所示,最前面是TX信号的结果,后面显示的是接收的RX眼图结果。

【5】在可以对显示的信号眼图进行打开或者关闭,通过点击进行关闭显示,或者打开显示。能够各个接收和发送的仿真眼图进行查看和分析。

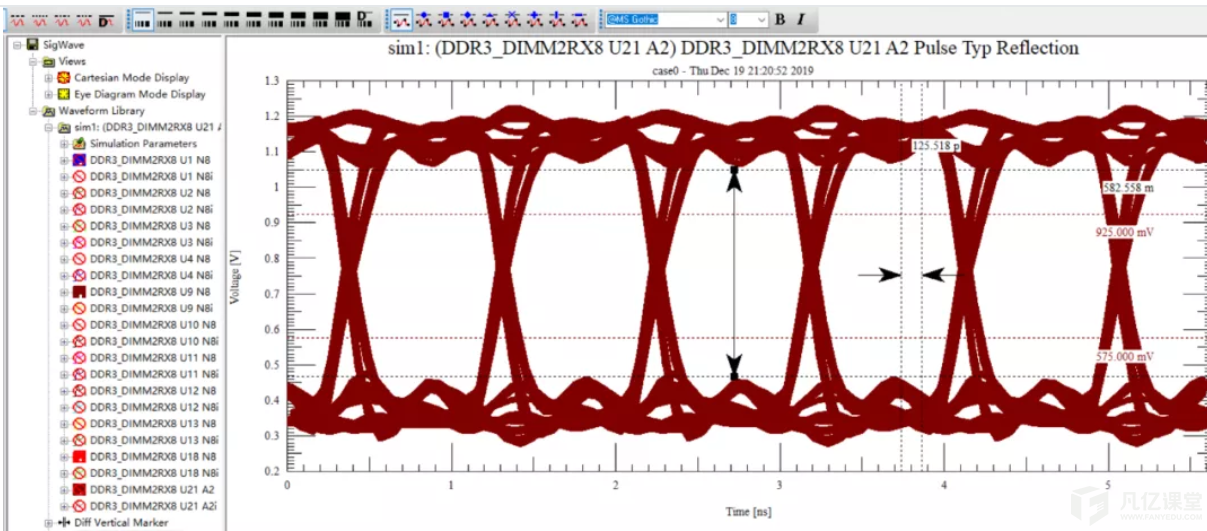

【6】使用标尺和标注对仿真完成的眼图进行标注和测量。

【7】经过测量可以看到眼图的宽度在1.787ns,眼图的高度高度在750mV,黑色最后一组RX接收里面信号的过冲最大。

在眼图模式下修改UI为1876ps,对眼图按照3个周期进行整理,整理完成后眼图效果就能够看到周期性的仿真结果显示。

通过内置的DDR3模板,可以对显示的结果进行测量,自动给出测量的结果。

Allegro软件中进行高速信号仿真分析的方法,操作简单,功能强大,对于提升设计效率以及设计的准确性验证都有很大的帮助,阅读完这篇文章的小伙伴可以自己去试一试这个信号质量仿真分析功能,以便于进一步提高工作效率。

暂无评论