凡亿教育-乐乐

凡事用心,一起进步打开APP

公司名片FPGA等可编程逻辑器件设计流程详解

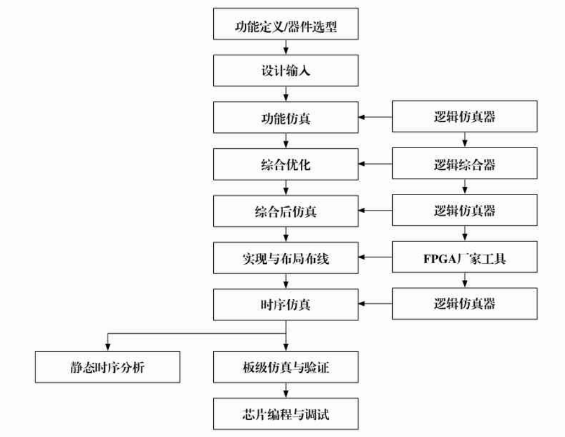

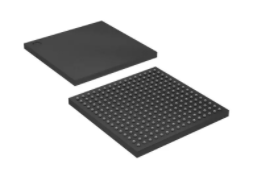

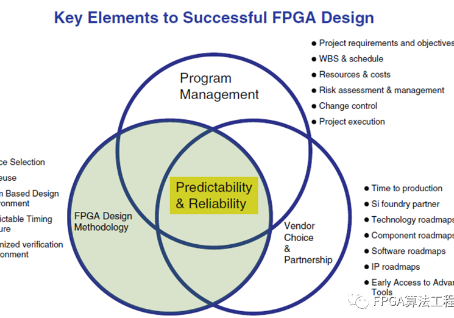

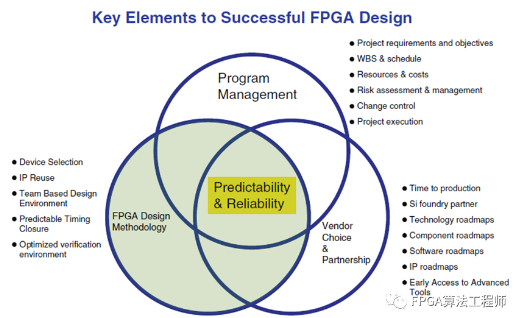

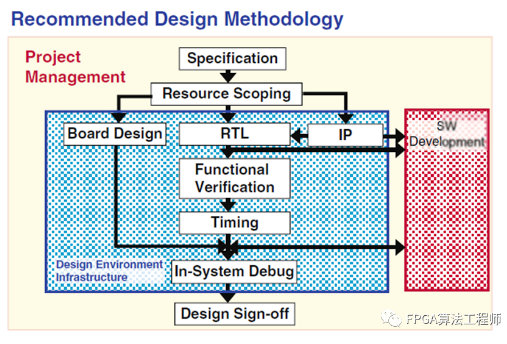

要设计可编程逻辑器件,如FPGA、CPLD等,并非一件易事,尤其是对于刚入FPGA的初级工程师来说,那么为了能够设计出一件优秀的可编程逻辑器件产品,我们该如何进行设计?

一般来说,通常可将FPGA/CPLD设计流程归纳总结为以下7个步骤,基本上与ASIC设计有相似之处。

1、设计输入

以Verilog或VHDL编写代码为主。

2、前仿真(功能仿真)

设计的电路必须在布局布线前验证电路功能是否有效。(ASIC设计中,该步骤被称为第一次Sign-off)PLD设计中,偶尔跳过该步骤。

3、设计编译(综合)

设计输入之后将有一个从高层次系统行为涉及向门级逻辑电路设转化成翻译过程,即把设计输入的某种或基几种数据格式(网表)转化成软件可识别的某种数据格式(网表)。

4、优化

对于上述综合生成的网表,根据布尔方程功能等效的原则,用更小更快的综合结果替代一些复杂的单元,并与制定的库映射成新的网表,这是减小电路规模的必经之路。

5、布局布线

6、后仿真(时序仿真)

需要利用在布局布线中获得的精确参数再次验证电路的时序。(在ASIC设计中,该步骤被称为第二次Sign-off)

7、生产

布线和后仿真完成后,就可以开始FPGA或CPLD芯片的投产。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论