小白初接触FPGA逻辑芯片,可能会困惑EPLD、CPLD、FPGA等这些英文名词,也不知道它们有什么用,所以本文将为小白一一解答这些问题,希望对小伙伴们有所帮助。

1、GAL(Generic Array Logic)

全称为通用阵列逻辑,是1985年Lattice公司最先发明的可电擦写、可重复编程、可设置加密位的PLD。GAL在PAL基础上,采用了输出逻辑宏单元形式E2CMOS工艺结构。具有代表性的GAL芯片有GAL16V8、GAL20V8,这两种GAL几乎能够仿真所有类型的PAL器件。在实际应用中,GAL器件对PAL器件仿真具有百分之百的兼容性,所以GAL几乎完全代替了PAL器件,并可以取代大部分SSI、MSI数字集成电路,如标准的54/74系列器件,因而获得广泛应用。

2、EPLD(Erasable PLD)

EPLD是20世纪80年代中期Altera公司推出的基于UVEPROM和CMOS技术的PLD,后来发展到采用E2CMOS工艺制作的PLD。EPLD基本逻辑单元是宏单元。宏单元由可编程的与或阵列、可编程寄存器和可编程l/o三部分组成。从某种意义上讲EPLD是改进的GAL,它在GAL基础上大量增加输出宏单元的数目,提供更大的与阵列,灵活性较GAL有较大改善,集成密度大幅度提高,内部连线相对固定,延时小,有利于器件在高频率下工作,但内部互连能力弱。世界著名的半导体器件公司如Altera.Xilinx、AMD、Lattice均有EPLD产品,但结构差异较大。

3、CPLD(Complex PLD)

CPLD是20世纪80年代末Lattice公司提出了在线可编程(lSP,In System Programmability)技术以后于20世纪90年代初出现的。CPLD是在EPLD的基础上发展起来的,采用E2CMOS工艺制作,与EPLD相比,增加了内部连线,对逻辑宏单元和l/O单元也有重大的改进。CPLD至少包含三种结构:可编程逻辑宏单元、可编程I/O单元和可编程内部连线。部分CPLD器件内部还集成了RAM、FIFO或双端RAM等存储器,以适应DSP应用设计的要求。其典型器件有Altera的MAX7000系列,Xilinx的7000和9500系列,Lattice的PLSI/ ispLSI系列和AMD的MACH系列。

4、FPGA(Field Programmable Gate Array)

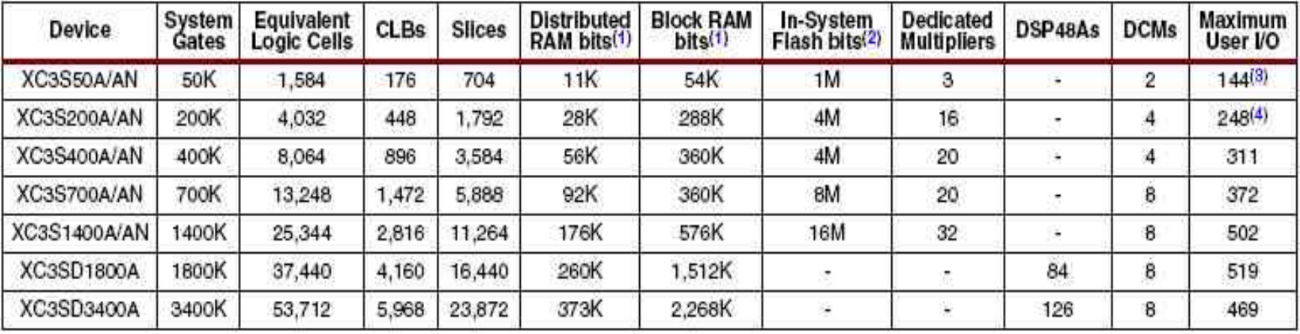

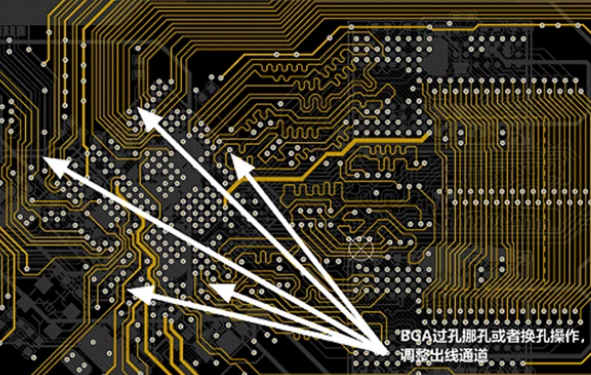

FPGA是Xilinx公司1985年首家推出的,它是一种新型的高密度PLD,采用CMOS-SRAM工艺制作。其结构与门阵列PLD不同,内部由许多独立的可编程逻辑模块(CLB)组成,逻辑块之间可以灵活地相互连接。FPGA的结构一般分为三部分:可编程逻辑块、可编程l/○模块和可编程内部连线。CLB的功能很强,不仅能够实现逻辑函数,还可以配置成RAM等复杂的形式。配置数据存放在片内的SRAM或者熔丝图上,基于SRAM的FPGA器件工作前需要从芯片外部加载配置数据。配置数据可以存储在片外的EPROM或者计算机上,设计人员可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场可编程。FPGA出现后受到电子设计工程师的普遍欢迎,发展十分迅速。Xilinx、 Altera和Actel等公司都提供高性能的FPGA芯片。

暂无评论