凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片GAL16V8芯片的引脚图及原理图详解

为帮助萌新更好地学习FPGA芯片,本文将重点谈谈GAL16V8芯片,分享GAL16V8的引脚图、原理图等基础知识。

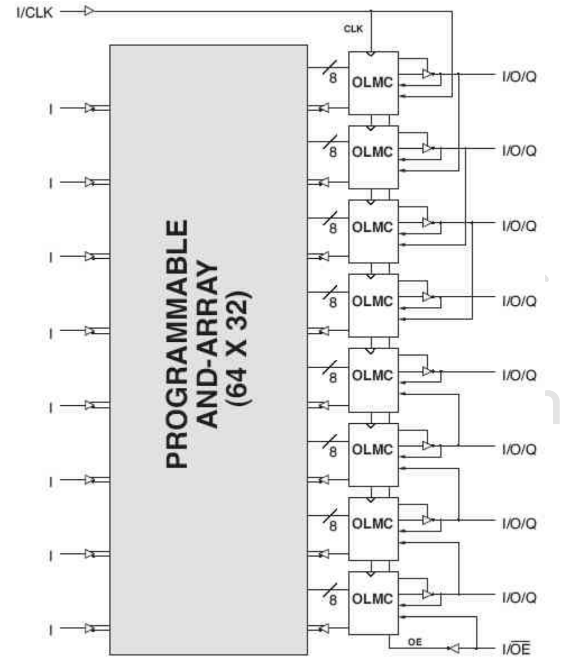

1、GAL16V8的输入输出

8个输入缓存器和8个输出反馈/输入缓冲器

8个输出逻辑宏单元OLMC,8个三台缓冲器,每个OLMC对应1个I/O引脚。

由8*8个与门构成的与阵列,共形成64个乘积项,每个与门有32个输入项,由8个输入的原变量、反变量(16)和8个反馈信号的原变量、反变量(16)组成,故可编程与阵列共有32*8*8=2048个可编程单元。

时钟CK和三态输出选通信号OE的输入缓冲器。

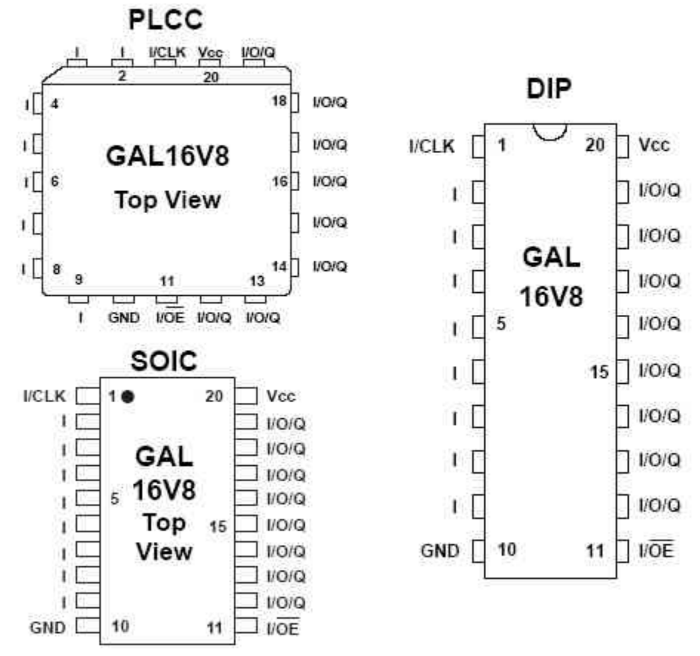

2、GAL16V8的引脚图及原理图

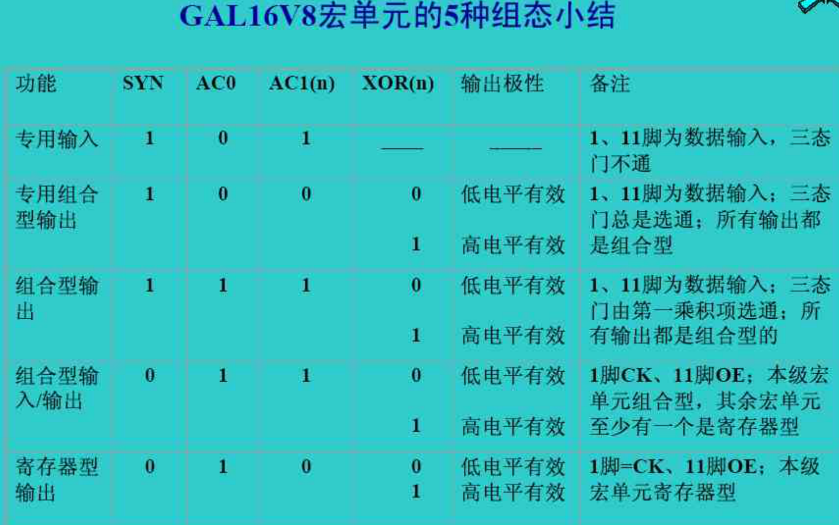

3、GAL16V8宏单元

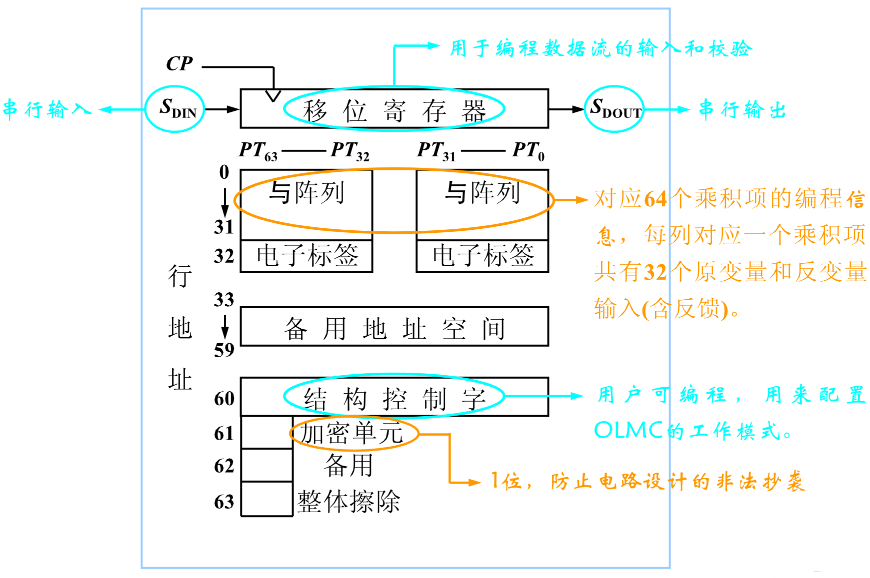

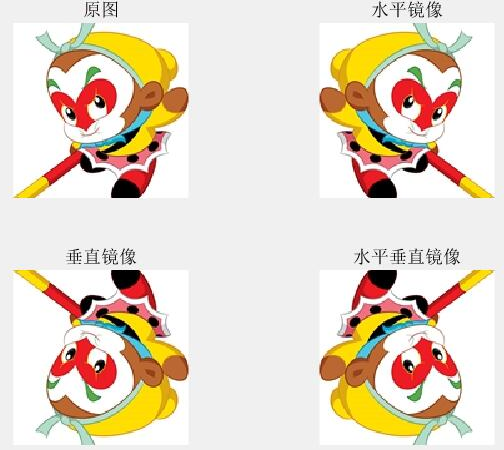

4、GAL16V8行地址映射

GAL的逻辑功能、工作模式都是靠编程来实现的。编程时写入的数据按行安排,GAL16V8 共分64行,供用户使用的有36行。上图表示GAL16V8编程单元的地址分配和功能划分情况,因为它并不是实际的空间布局图,所以称为行地址映射图。

第0~31行对应与逻辑阵列的编程单元,编程后可产生0~63共64个乘积项。

第33~59行是厂家保留的地址空间,用户不能利用。

第60行是结构控制字,共有82位,用于设定8个OLMC的工作模式和64个乘积项的禁止。

第61行是一位加密单元。这一位被编程以后,将不能对与逻辑阵列作进一步的编程或读出验证因此可以实现对电路设计结果的保密。只有在与逻辑阵列被整体擦除时,才能将加密单元同时擦除。但是电子标签的内容不受加密单元的影响,在加密单元被编程后电子标签的内容仍可读出。

第63行只包含一位,用于整体擦除。

对GAL编程时是逐行进行的,被编程的数据从第9脚以串行方式送入64位移位寄存器,寄存器装满一次,就对GAL阵列写一行。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论