一个layout工程师学习信号完整性之路

上一篇文章介绍IBIS的基本构造,下面简单整理IBIS中一些常用的概念,以便于我们在使用IBIS知道这些都代表什么意思:

IBIS中术语解释

R_pkg、L_pkg、C_pkg:封装参数

C_comp:为硅片上脚的压焊盘电容 (结电容)

C_pin , R_pin , L_pin : 引脚的RLC参数

signal_name:信号名称

model_name:模型名称

Model_type I/O:模型类型为输入和输出

Polarity Non-Invertin:极性 没有极性

Enable Active_low:使能为低电平有效

Vinl:低电平

Vinh:高电平

Vmeas:端接电压

Cref\Vref\Rref:cell寄生参数

Pullup Reference:上拉

Pulldown Reference:下拉

POWER Clamp Reference:电源钳位

GND Clamp Reference:GND钳位

threshold:阈值

扫描电压范围对于GND钳位是-VDD至VDD

扫面电压范围对于电源钳位是VDD至2VDD

扫描电压范围与数据钳位是-VDD至2VDD

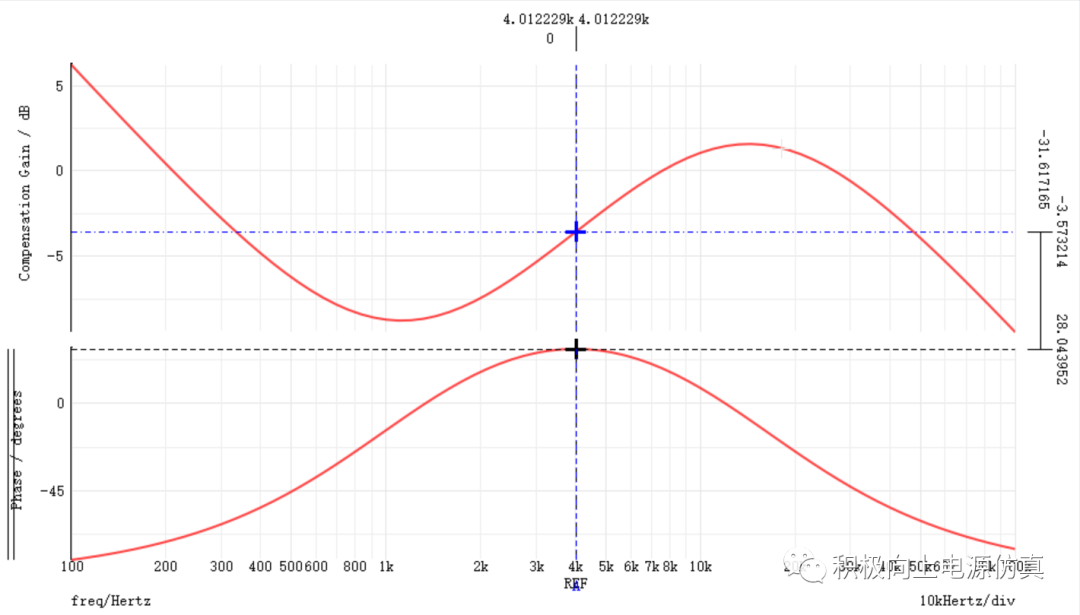

斜坡频率就是电压和电流的关系

电压和电流-伏安特性曲线

电压和时间的关系代表I/O变化的速度

钳位:钳位是指将某点的电位限制在规定电位的措施,是一种过压保护技术。产生这个措施的那些电路叫做钳位电路(clamping circuit)。钳位电路的作用是将周期性变化的波形的顶部或底部保持在某一确定的直流电平上。从而提高整个电路的工作稳定性。在钳位电路中存在钳位二极管(clamping diode),钳位二极管,产生钳位电压(Clamping voltage)

Power_Clamp 为低端ESD结构的V/I 曲线

GND_Clamp 为低端ESD结构的V/I 曲线

Pullup, Pulldown 为高电平和低电平状态的V/I曲线。

Ramp 为上升沿和下降沿的摆率(dv/dt)。指的是输出电压从20%–80%的电压输出幅度所用的时间。为了更加准确地描述上升沿和下降沿的过程,有上升沿和下降沿的V/T 曲线。

dV/dT_r, dV/dT_f:输出上升沿和下降沿的摆率。即:从20%80%,或从80%20% 电压输出幅度所需的时间。

Clamp 电流: Power/Ground Clamp的电流和Pull-up/Pull-down的电流都是在稳态下得到的, 在仿真时这四者也是一同拿来做load-line的计算的;所不同处, 因为clamp所表示的是ESD的保护电路故其为总是存在 (always on), 当这两组表格存在时, 为避免其又被在PU/PD表格里又再被算一次 (double counting), 在做后处理时需把这部份自后者中移除。若要简化这个麻烦, 其实一个有IO功能的buffer 在被拿来做输出buffer使用时便可直接以output type buffer来建模而非io type buffer而可略过此一部份。

IT 电流(Power aware): 这些是为了描述buffer 在非理想供电或接地情况下的运作而需加入的资料, 其应用则主要用在如DDR DQ的单端点模型里, 因为它们对PDN的扰动所造成的时间影响最为敏感。对于诸如SERDES的差分模型而言, 因为在P及N点的输出端会被PDN同样的影响, 在相减之下效应就抵消了, 所以影响很小而未必有此需要。最后, IT在瞬态的部份其实是和VT一同仿真的, 其只是在PAD端加上一个电流的Probe便可取得相对应的资料, 而且这IT和VT的各点间是需同步的, 所以只要在同一仿真里就可完成。

下面是从IBIS官网下载的输入、输出

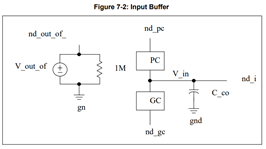

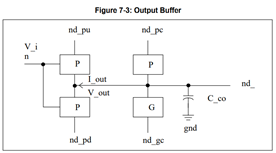

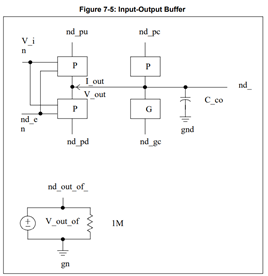

输入输出的模型结构:

以上资料主要是本人在仿真流程中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!!

暂无评论