在电子设备中,接地是控制干扰的重要手段之一,很多工程师都会使用接地和屏蔽结合来抑制,可解决大多数的电磁干扰问题,但部分小白不太清楚如何通过地线设计来抑制电磁干扰,所以本文将分享抑制电磁干扰的电路地线设计方法,希望对小伙伴们有所帮助。

一般来说,电子设备中地线结构大致上有系统地、机壳地(屏蔽地)、数字地(逻辑地)和模拟地等,在底线设计中应注意以下几点:

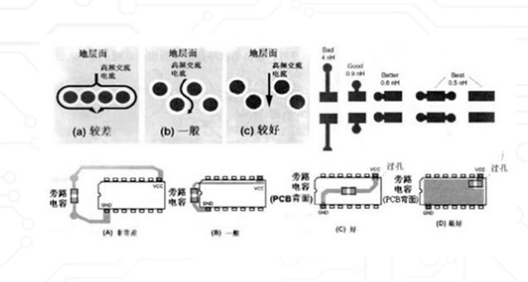

1、正确选择单点接地与多点接地

在低频电路中,信号的工作频率小于1MHz,它的布线和器件间的电感影响较小,而接地电路形成的环流对干扰影响较大,因而应采用一点接地。当信号工作频率大于10MHz时,地线阻抗变得很大,此时应尽量降低地线阻抗,应采用就近多点接地。当工作频率在1-10MHz时,如果采用一点接地,其地线长度不应超过波长的1/20,否则应采用多点接地法。

2、将数字电路与模拟电路分开

电路板上既有高速逻辑电路,又有线性电路,应使它们尽量分开,而两者的地线不要相混,分别与电源端地线相连。要尽量加大线性电路的接地面积。

数字和模拟地的连接最好采用平衡接地。在两者之间加匹配的穿芯磁珠。

3、尽量加粗接地线

若接地线很细,接地点位则随电流的变化而变化,致使电子设备的定时信号电平不稳,抗噪声性能变坏,因此应将接地线尽量加粗,使他能通过三位位于音质电路板的允许电流。如有可能,接地线的宽度应大于3mm。

在没有宽度可以增加时,可以考虑增加厚度,是指在走线上加锡。

4、将接地线构成闭环路

设计只由数字电路组成的印制电路板的地线系统时,将接地线做成闭环路可以明显的提高抗噪声能力。其原因在于:印制电路板上有多种集成电路元件,尤其是耗电多的元件时,因为受到接地线粗细的限制,会在地结上产生较大的电位差,引起抗噪声能力下降,若将接地结构构成环路,则会缩小电位差值,提高电子设备的抗噪声能力。

暂无评论