凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片数字电路设计和模拟电路设计有什么不同?

集成电路问世以来,虽经历时间不长,但应用广泛,逐渐成为国家的重点培养的核心产业之一。一般来说,集成电路的电路/逻辑设计主要分为数字电路设计和模拟电路设计,所以它们有哪些不同?

1、数字电路设计

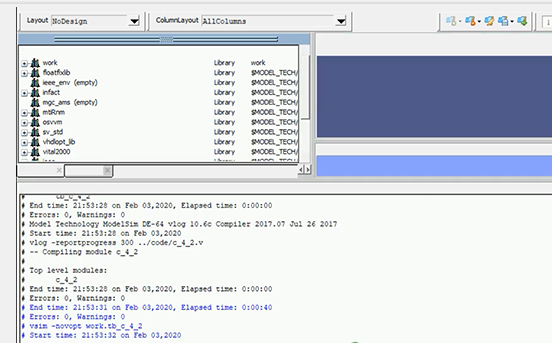

数字电路设计一般是从RTL(寄存器传输级)开始的,设计者根据上一阶段得到的各模块的规范,用Verilog/VHDL语言完成RTL代码。

RTL代码完成后,工程师可借助nLint等语法检查工具改进代码质量,然后进行RTL仿真,以保证设计功能争取。RTL仿真无误后,用逻辑综合工具将RTL代码转成门级网表,再将门级网表交由后端进行布局布线。

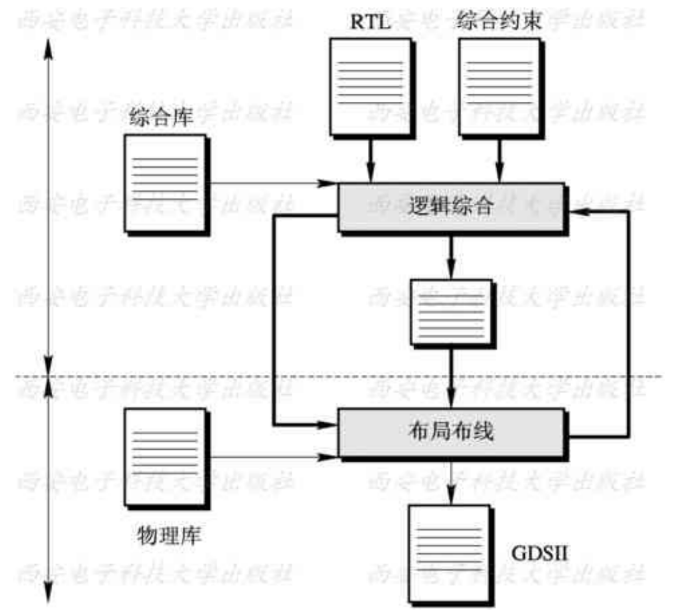

如图所示,该图是数字电路设计的具体流程,虚线以上是逻辑设计,虚线以下是物理设计。

在数字电路设计阶段,设计者根据设计规范,需要完成:写RTL代码;将RTL代码综合为门级网表。如果需要,加入JTAG/扫描链/clock gating等内容;进行时序检查、等价性检查、测试覆盖率估计、功耗分析等。

2、模拟电路设计

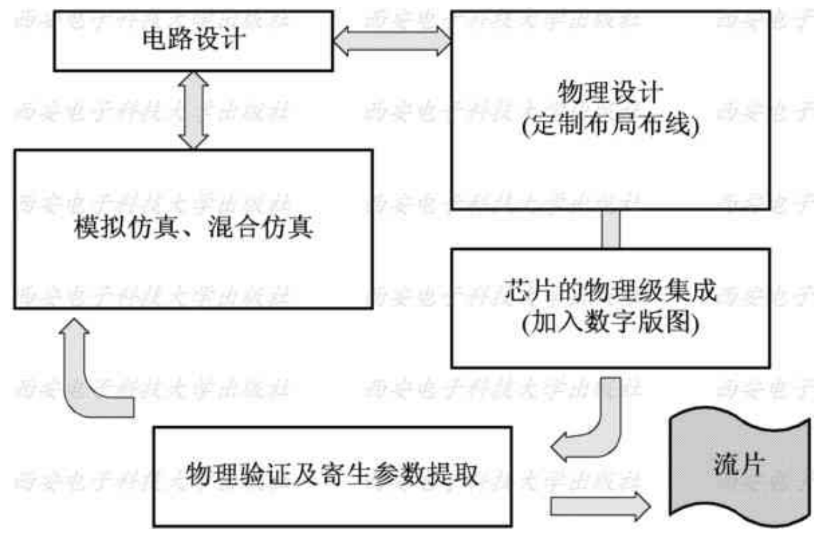

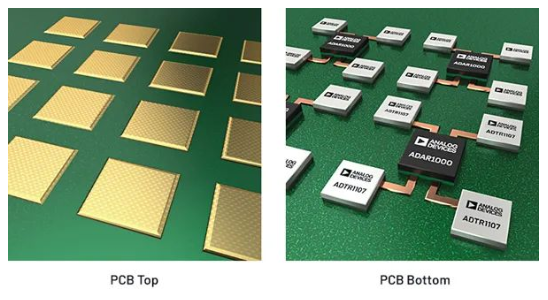

模拟电路的设计一般是从晶体管级开始,采用手工设计生成最终网表。如图所示,该图是模拟电路的设计流程:

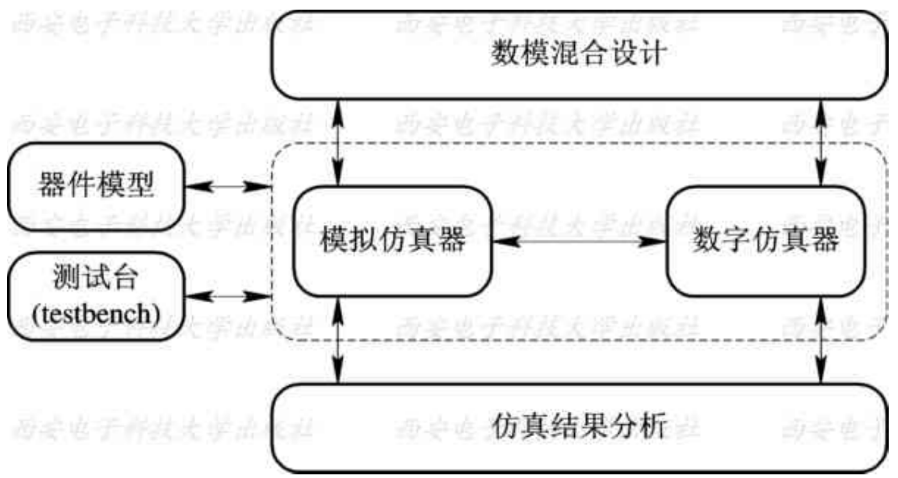

实际上,IC系统往往是数模混合系统,数字IC与模拟IC单独设计、各自验证的流程导致芯片开发效率降低,数模混合仿真的具体流程如图所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论