凡亿教育-小米

凡事用心,一起进步打开APP

公司名片CPLD芯片的内部结构及电路图分析

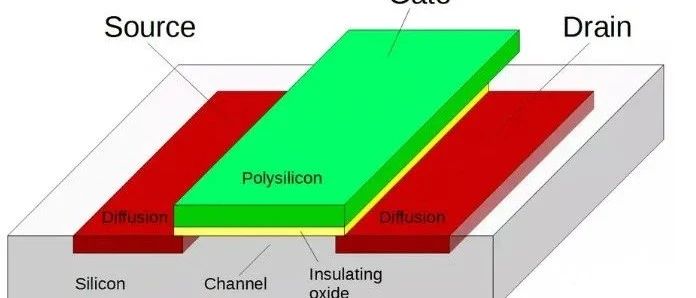

随着微电子技术的发展,FPGA逐渐替代PDL等可编程逻辑器件应用在各个领域,但CPLD因其独特的特点性质,仍然比FPGA更适合应用在部分领域,但由于很多小白没装没接触过CPLD芯片,也不清楚其结构,所以本文将探讨CPLD芯片的内部结构。

CPLD有完全可编程的与/或阵列及宏单元库构成。与/或阵列是可重新编程的,可以实现多种逻辑功能。宏单元则是可实现组合或时序逻辑的功能模块,同时还提供了真值或补码输出和以不同的路径反馈等额外的灵活性。

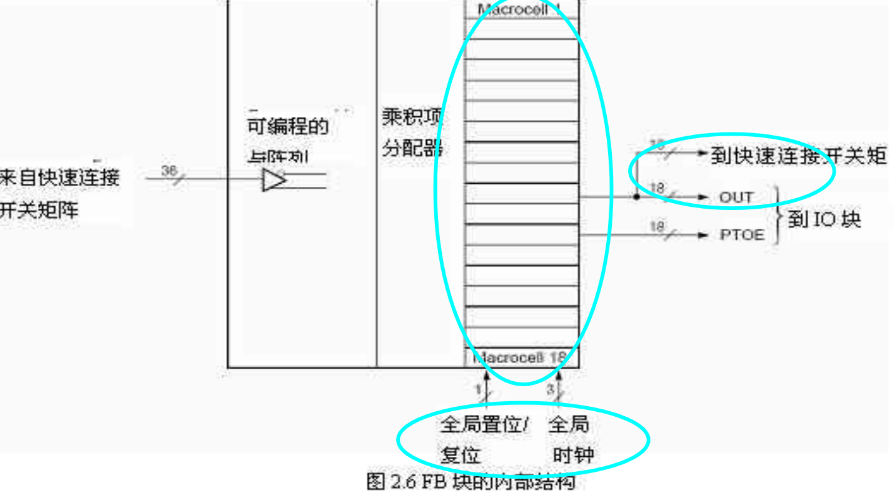

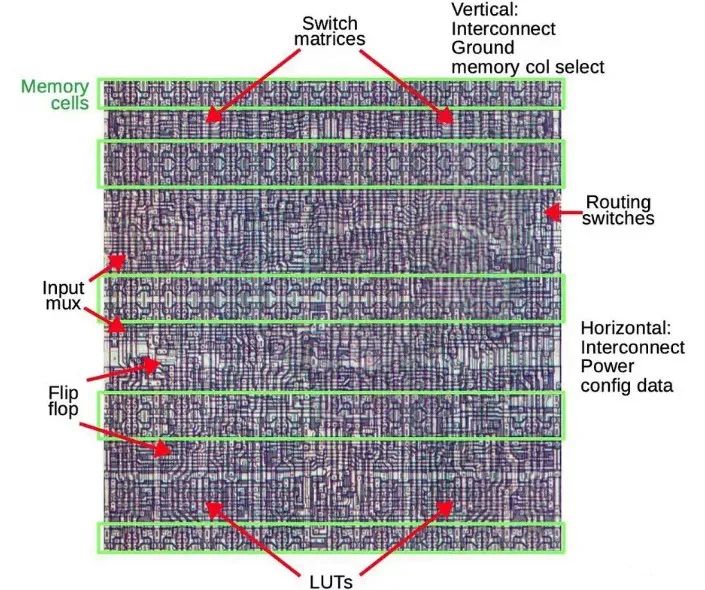

1、CPLD的内部结构图

2、CPLD芯片内部结构图——功能块

FB内部的逻辑使用积之和SOP描述,36个输入提供了72个镇和互补信号到可编程的“与”阵列来生成90个乘积项。最多可用的90个乘积项可通过乘积项分配器分配到每一个宏单元。

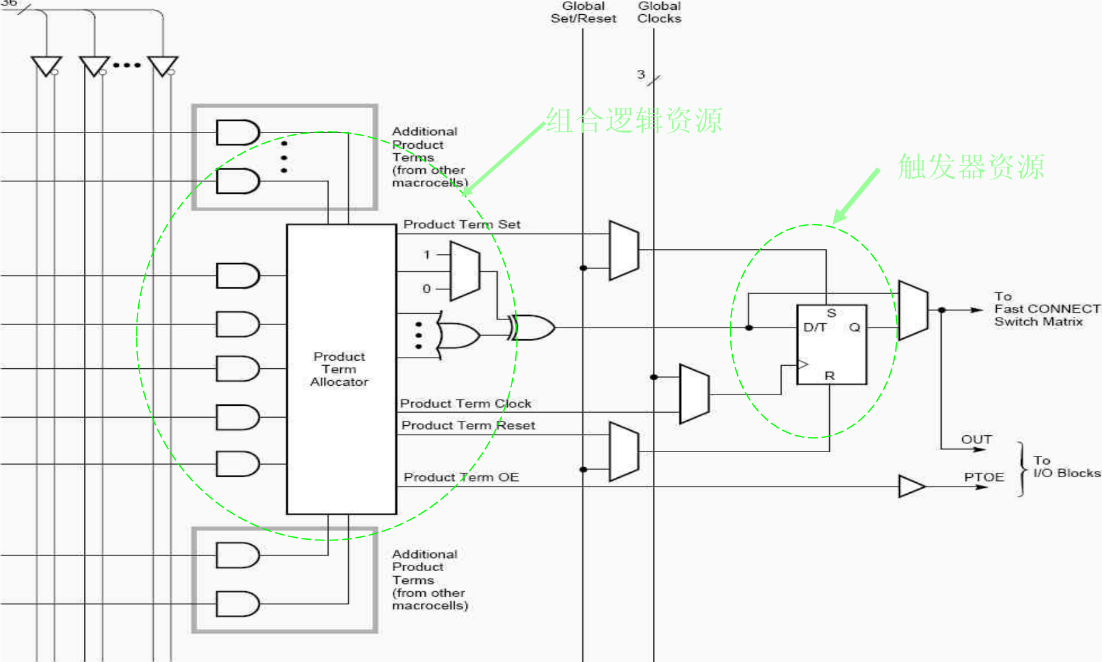

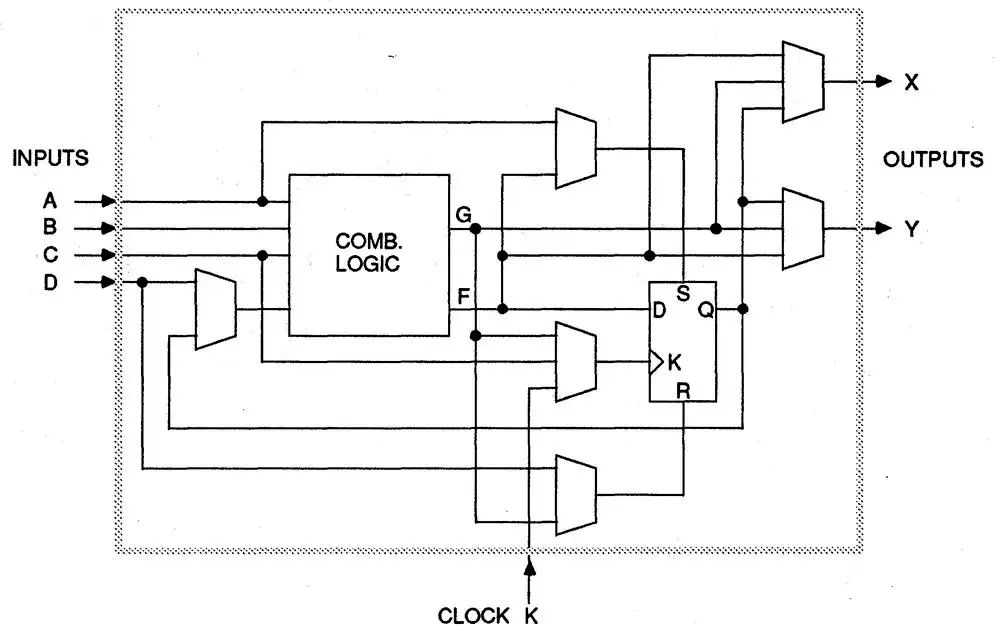

3、CPLD芯片内部结构——宏单元

从数字电路的知识知道,任何一个数字系统是由组合逻辑电路和时序电路构成的。所以宏单元应该是CPLD芯片最重要的功能单元。因为数字系统的逻辑功能是在宏单元内实现的。

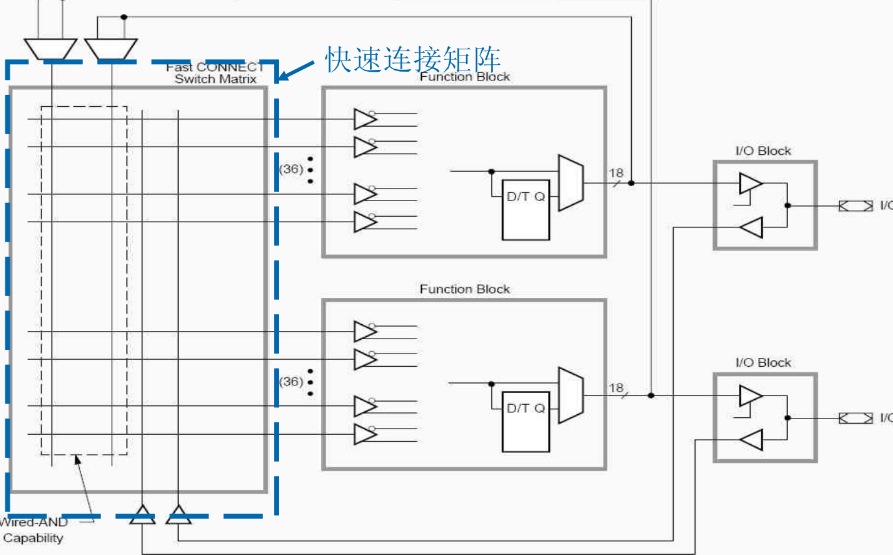

4、CPLD芯片内部结构——快速连接矩阵

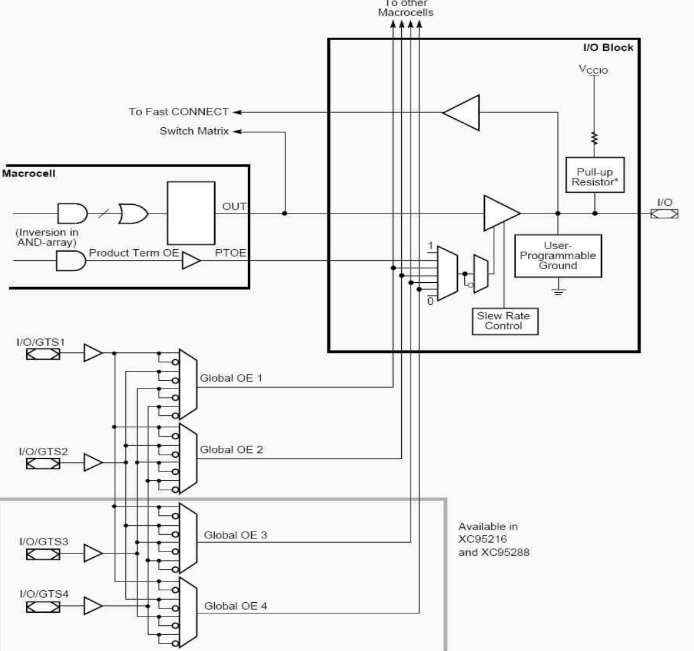

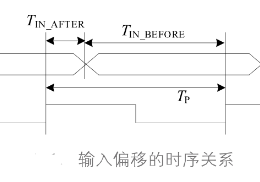

5、CPLD芯片内部结构——IO内部逻辑

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论