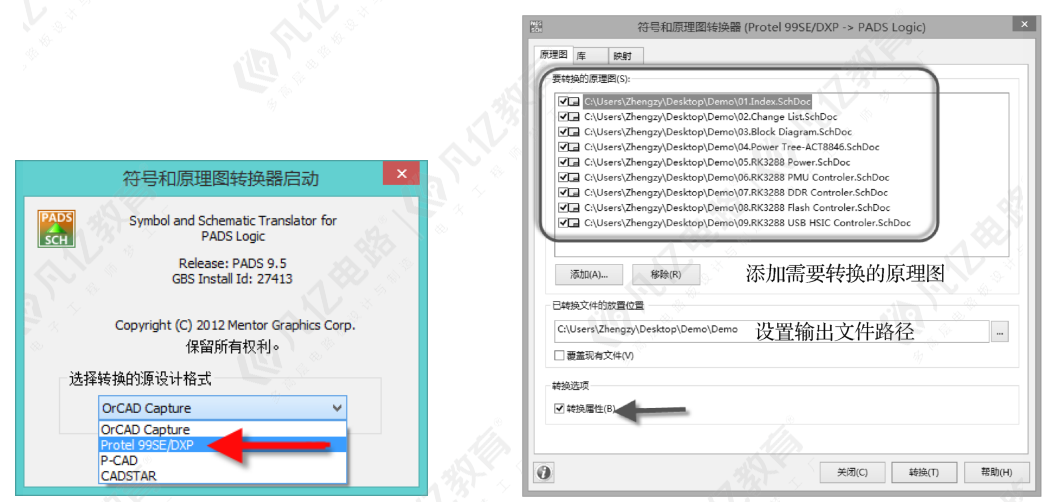

xSignals功能可显著提高设计效率。利用xSignals向导即可自动进行高速设计的长度匹配,它可以自动分析T形分支、元件、信号对和信号组数据,大大减少了高速设计配置时的时间消耗。

1.手工法创建xSignals

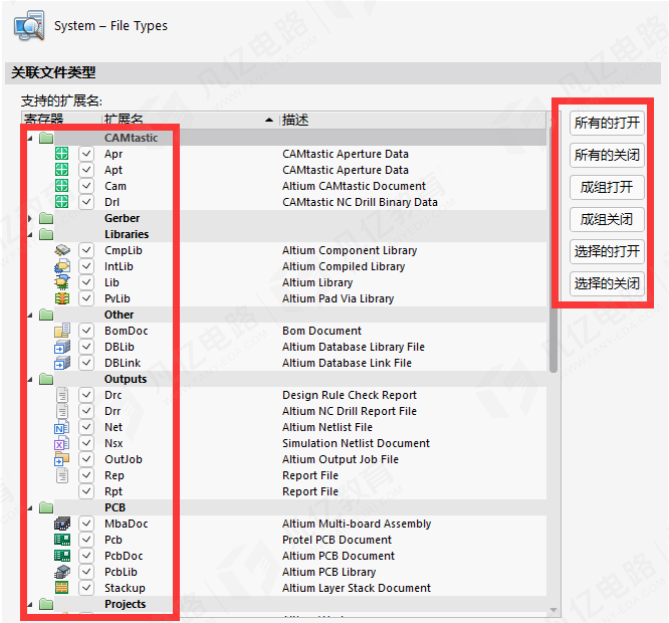

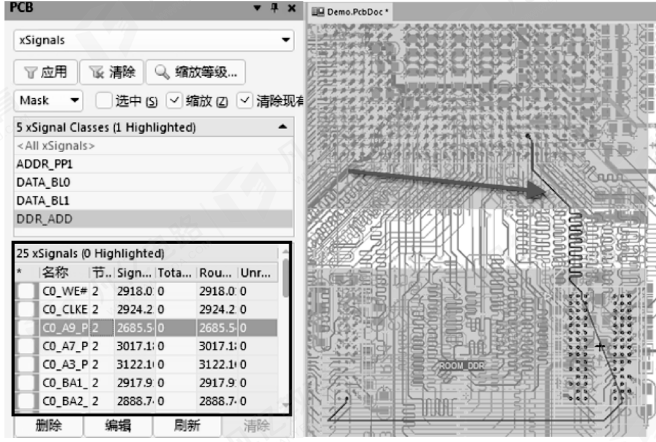

(1)在PCB设计交互界面的右下角执行命令“Panels-PCB”,选择“xSignals”,打开“xSignals”面板栏,如图10-121所示,在这里有默认的“All xSignals”,可以在这里单击创建xSignal类,在类窗口中单击鼠标右键,选择“添加类”选项,添加一个以“DDR_ADD”为例的xSignal类。

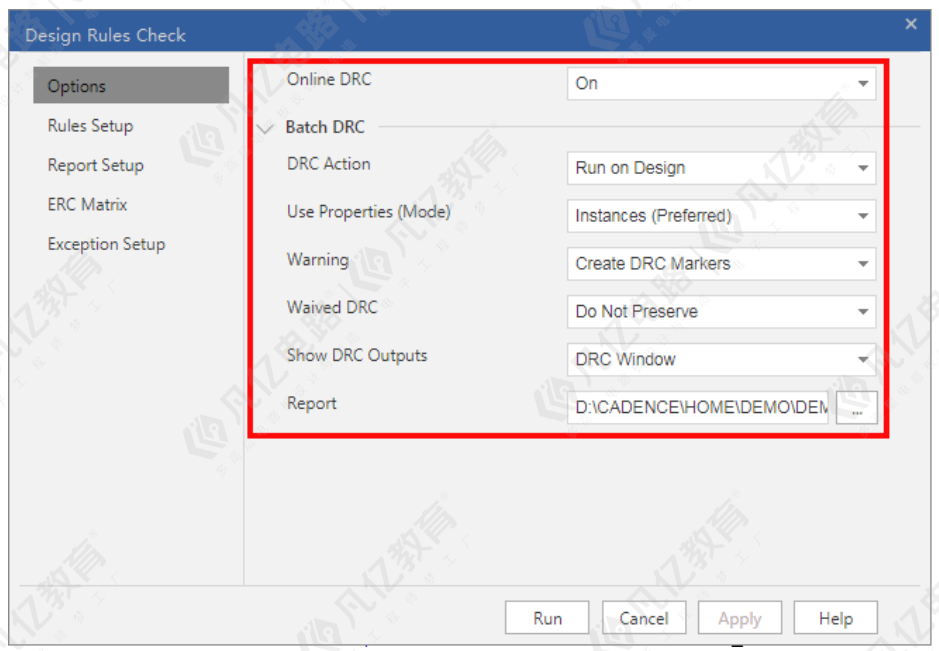

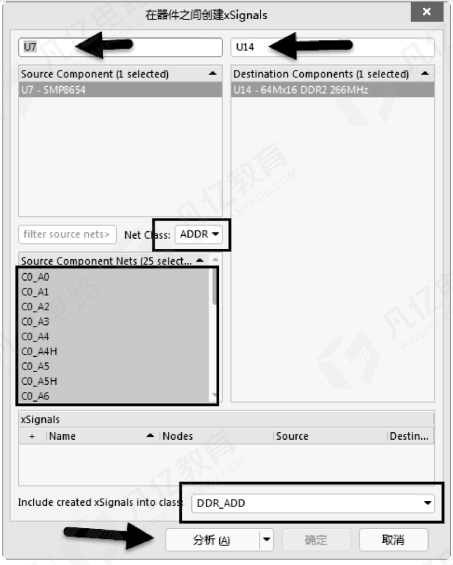

(2)执行菜单命令“设计-xSignal-创建xSignals”,如图10-122所示,进入xSignals添加匹配界面,如图10-123所示。

图10-121 添加xSignal类 图10-122 创建xSignals

图10-123 xSignals添加匹配界面

① 图10-123中上方两个箭头处输入第一匹配的元件位号和第二匹配的元件位号,这里选择“U7”和“U14”,即CPU和第一片DDR。

② Net Class:如果之前创建了网络类,可以通过这里滤除一些网络,从而精准地筛选出需要添加到xSignals中的网络。

③ Include created xSignals into class:把这些适配的网络添加到刚创建的xSignal类中。

(3)单击“分析”按钮,系统即可自动分析出哪些网络需要添加到xSignals中,单击“OK”按钮,完成添加,如图10-124所示。

图10-124 添加成功的xSignals

2.向导法创建xSignals

如果存在很多xSignals需要创建,可以通过xSignal向导,并利用元件与元件的关联性进行创建。

(1)执行菜单命令“设计-xSignal-运行xSignal向导”,打开xSignal向导,如图10-125所示,根据向导按“Next”按钮。

图10-125 xSignal向导

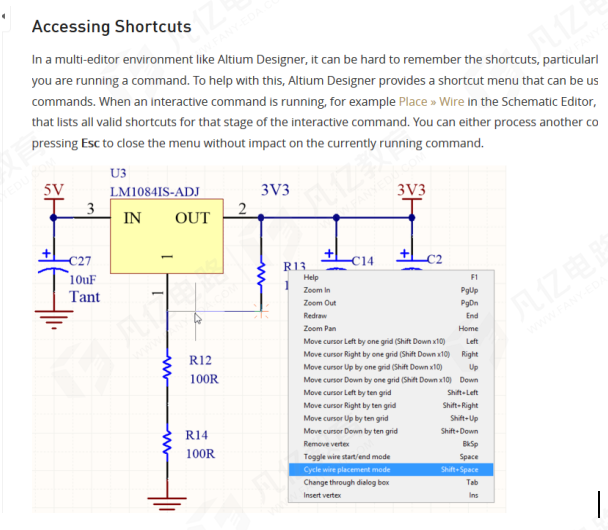

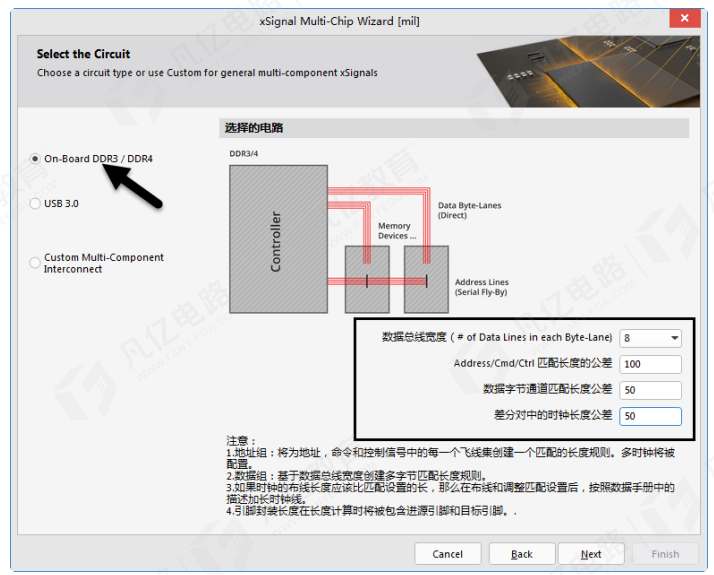

(2)进入如图10-126所示的“Select the Circuit”界面,选择创建xSignals的应用单元,此处提供3种选择。

图10-126 选择应用单元及误差填写

① On-Board DDR3/DDR4:有DDR3或者DDR4类型的板子。

② USB 3.0:含有USB 3.0的板卡。

③ Custom Multi-Component Interconnect:自定义选择类型。

因为方法类似,这里以DDR3/4的板卡类型为例进行说明。

l 数据总线宽度(# of Data Lines in each Byte-Lane):选择数据位类型,一般是8位或者16位,具体根据DDR来进行选择。

l Address/Cmd/Ctrl匹配长度的公差:填写地址线/控制线的匹配误差,DDR一般填写100mil,具体请详细参考DDR的规格要求。

l 数据字节通道匹配长度公差:填写数据线之间的误差,DDR一般填写50mil,具体请详细参考DDR的规格要求。

l 差分对中的时钟长度公差:填写差分时钟的误差,DDR一般填写50mil,具体请详细参考DDR的规格要求。

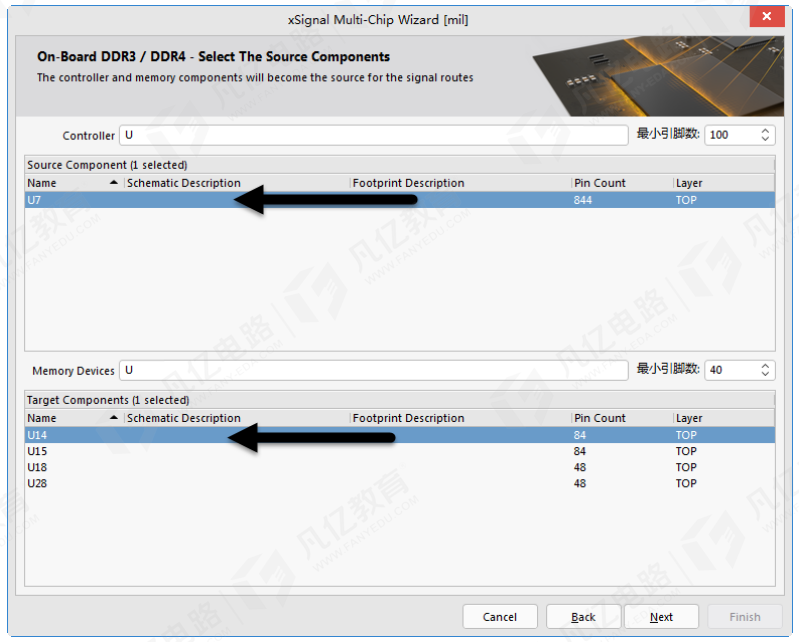

(3)单击图10-126中的“Next”按钮,进入如图10-127所示的界面,通过元件过滤功能,选择需要创建的第一个元件“U7”,即主控CPU,然后选择预知关联的第一片DDR“U14”,这之后单击“Next”按钮。

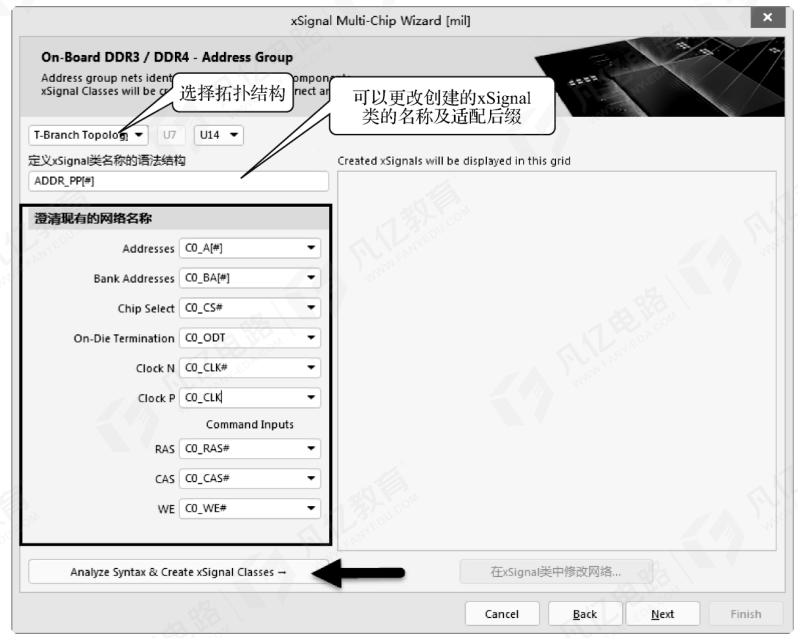

(4)进入如图10-128所示的界面,根据需要设置相关参数。

① T-Branch Topology:选择拓扑结构。

② 定义xSignal类名称的语法结构:自定义创建的xSignal类的名称和后缀。

③ 澄清现有的网络名称:选择地址线、控制线、时钟线总线的适配。

单击“Analyze Syntax & Create xSignal Classes”按钮,创建xSignal类,然后单击“Next”按钮。

图10-127 xSignals的元件关联选择

图10-128 地址线网络关联的适配

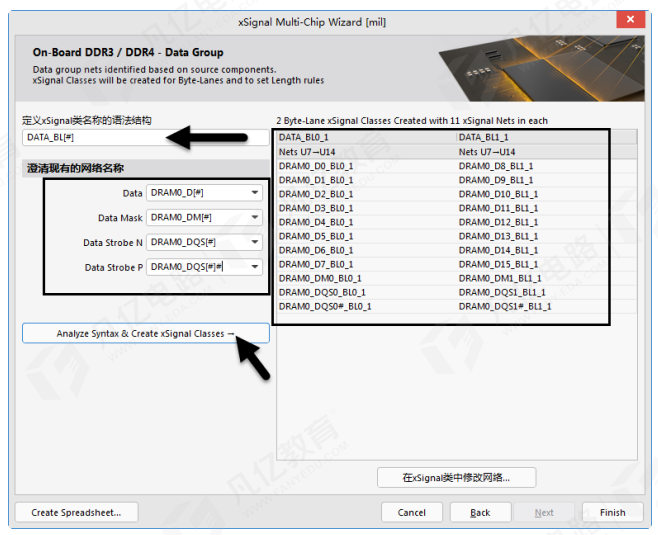

(5)进入如图10-129所示的界面,类比于地址线的适配方法,设置好数据线适配的参数。单击“Finish”按钮,完成U7—U14的xSignals的创建。

图10-129 数据线网络关联的适配

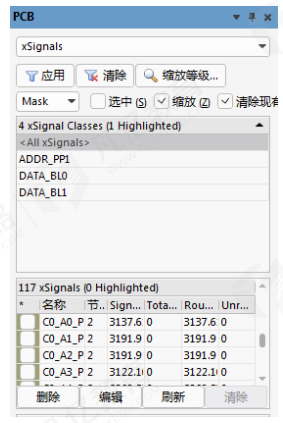

(6)在PCB设计交互界面的右下角执行命令“Panels-PCB”,选择“xSignals”,可以看到系统自动创建了3组xSignal类,单击其中的某一类,对其进行等长绕线,直到里面没有红色的标记为止,如图10-130所示。

图10-130 xSignal类等长数据列表

(7)依据上述方法,可以再创建CPU到另外一片DDR的xSignal类,分别进行等长。