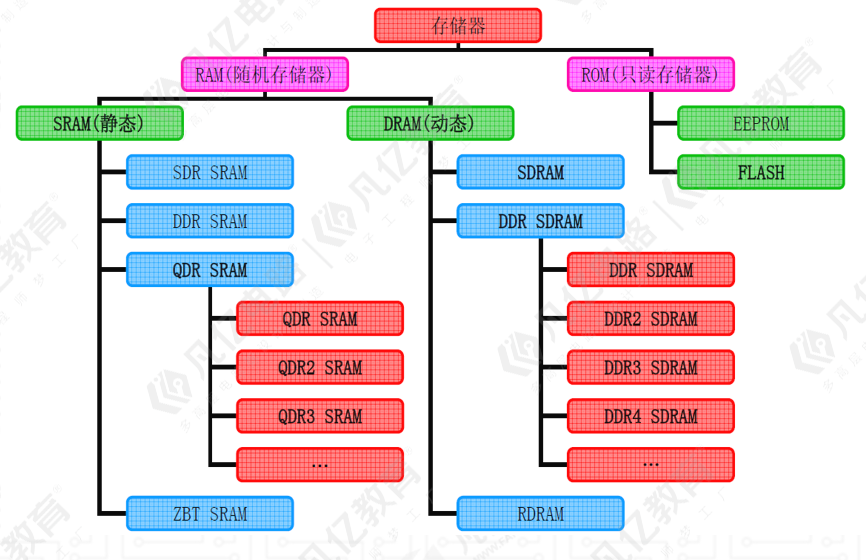

一、存储器的定义以及分类

RAM:Random Access Memory,随机存取存储器,也叫主存,是与CPU直接交换数据的内部存储器,可以随时读写,而且速度快通常作为操作系统或其他正在运行程序的临时数据存储介质。

特点:随机存取,访问速度快,易失性,断电以后保存在上面的数据会自动消失

分类:

SRAM:静态随机存储器,SRAM存放的信息在不停电的情况下能长时间保留,常作为Cache高速缓冲存储器。

DRAM:动态随机存储器,DRAM的缺点是需要刷新逻辑电路,且刷新操作时不能进行正常读,写操作。DRAM与SRAM相比具有集成度高、功耗低、价格便宜等优点,所以在大容量存储器中普遍采用,常作为主存储器。

SDRAM:同步动态随机存取内存。就是DDR,如DDR1、DDR2、DDR3、

– 同步(Synchronous ):指其总线工作在同步时序方式下,由同一时钟同步触发。

– 动态(Dynamic )是指存储阵列需要不断的刷新来保证数据不丢失;

– 随机(Access )是指数据不是线性一次顺序存储的,而是自由指定地址进行数据的读写。

ROM:Read-Only Memory 只读存储器

特点:只能读出不能随意写入信息

分类:

–PROM:可编程程序只读存储器,但是只可以编写一次

–EPROM:可抹除可编程只读存储器,可重复使用

–EEPROM:电子式可抹除可编程只读存储器,类似于EPROM但是摸除的方式是使用高电场完成。

二、Flash分类与工作原理

FLASH:Flash是一种非易失性内存,闪存的物理特性与常见的内存有根本性的差异,目前各类 DDR、SDRAM 或者 RDRAM 都属于挥发性内存,只要停止电流供应内存中的数据便无法保持,因此每次电脑开机都需要把数据重新载入内存;

闪存在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备存储介质基础。

分类:

→NOR FLASH,它的特点就是可以在芯片内执行,应用程序可以直接在闪存中运行,不必把代码读入系统RAM

→NAND FLASH,Nand-Flash存储器具有容量较大,改写速度快等优点,适用于大量数据的存储

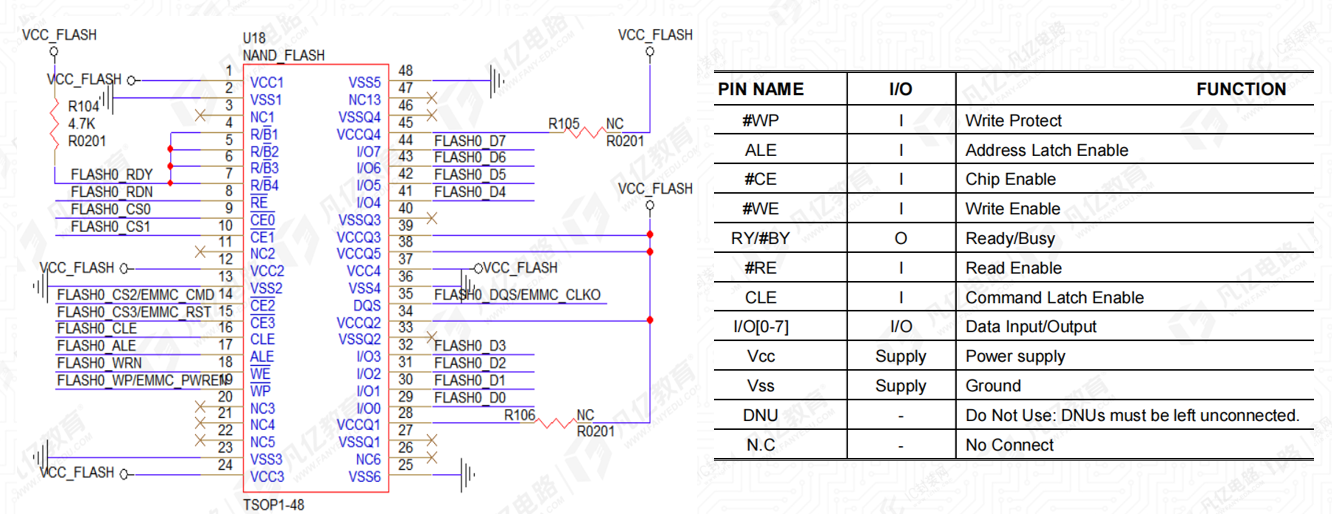

三、FLASH的信号管脚解读

1、I/O0 ~ I/O7用于输入地址/数据/命令,输出数据。

2、CLE为Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能。

3、ALE为Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能。

4、CE#Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作。

5、RE#为Read Enable,读使能,在读取数据之前,要先使CE#有效。

6、WE#为Write Enable,写使能,在写取数据之前,要先使WE#有效。

7、WP#为Write Protect,写保护。

8、R/B#为Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成。

9、Vcc为Power,电源。

10、Vss为Ground,接地。

11、N.C为Non-Connection,未定义,未连接。

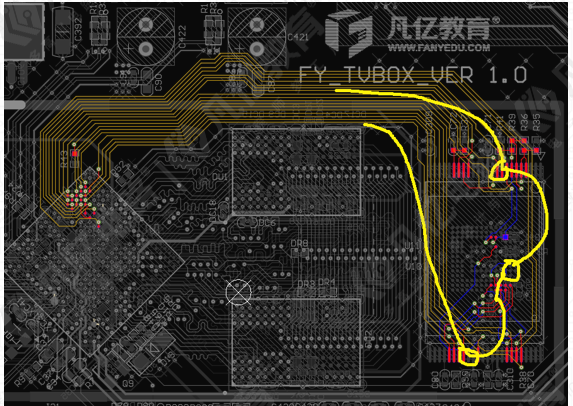

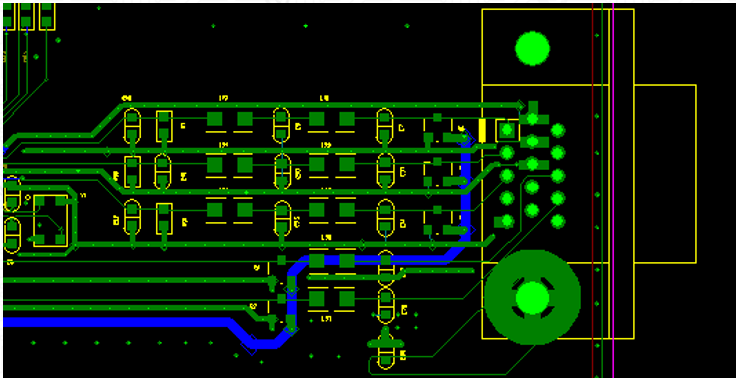

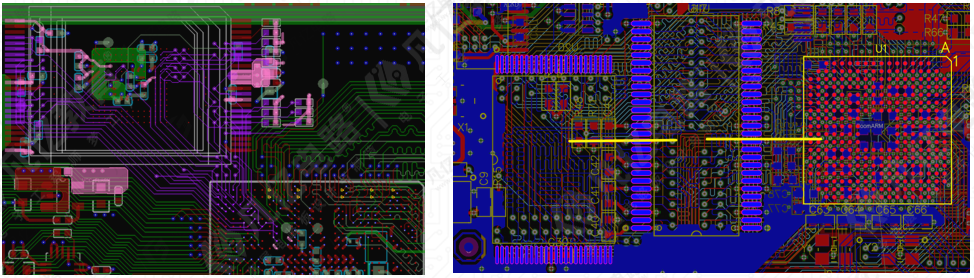

四、FLASH存储器PCB布局要求

PCB布局要求:

→NAND FLASH应靠近主控摆放,不宜太远;

→去耦电容均靠近FLASH芯片管脚摆放,均匀分配即可;

→RE、WE、DQS 信号若有串接电阻,靠近主控摆放,串阻与主控连接走线距离≤150mil;

→兼容设计了EMMC存储器,布局时直接叠放NAND FLASH中间,布线时注意拓扑结构;

→SDRAM与Flash布局采用菊花链拓扑结构

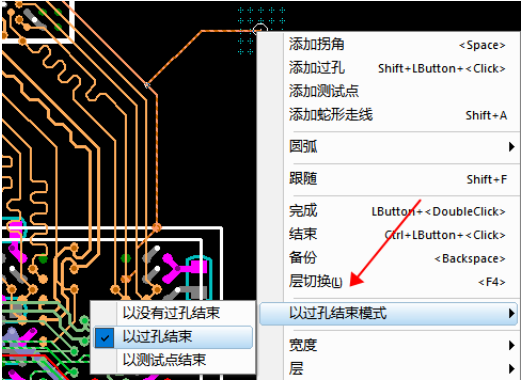

五、FLASH存储器PCB布局与布线要求

PCB布线要求:

→特性阻抗:单端50欧,没有差分信号;

→FLASH与主控芯片之间的走线长度小于3000mil;

→D0~D7 数据信号尽量同组同层,使用过孔的数量尽量相同;

→信号线的间距满足3W原则, CLK信号单独包地处理,地线每隔200mil打一个地过孔;

→所有信号线都不得跨分割,且有完整参考平面,换层时,若改变了参考层,要注意考虑增加回流地过孔或退藕电容;

→VCC/VCCQ 线宽不小于 12mil,或直接使用敷铜代替电源走线;

等长布线要求:

→D0~D7、RE、WE相对于DQS做等长,误差控制±100mil,使用过孔的数量尽量相等;

→兼容EMMC存储器,布线时优选按菊花链拓扑布线,注意走线拓扑结构