凡亿教育-莎莎

凡事用心,一起进步打开APP

公司名片Intel要研发一万亿个晶体管的处理器

随着微电子技术和信息技术的日益成熟,未处理日益复杂的数据和愈发严格的性能要求,芯片内嵌的晶体管数量翻倍增长,现在的芯片单个封装可以放入一千亿个晶体管,然而Intel要想实现更多。

近日,Intel被曝出要将芯片内部晶体管密度再翻10倍,达到万亿级,该消息是由Intel中国研究院院长宋继强透露出的,从2023年到2030年,晶体管密度要在8年时间里翻十倍,即实现2的3次方的提升。

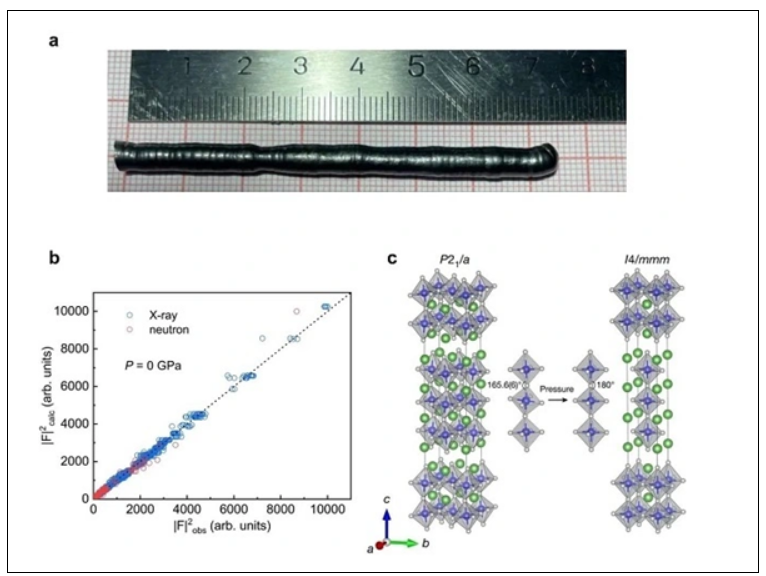

虽然这个目标相当激进,但Intel很有信息实现,宋继强表示,若要实现单个封装中集成一万亿个晶体管的芯片,可从良法米娜下手,一方面是,继续依靠晶体管微缩,如用厚度仅仅3个原子的超薄2D材料制作成更高效的GAA晶体管。另一方面是从3D封装技术入手,进一步提升整个涉笔中的晶体管总量。

按照Intel的路线规划图,Intel 4(即7nm工艺)预计将在2022年年底进入试产阶段,未来将用于第14代的Meteor Lake处理器。2023年下班年,将进入Intel 3(3nm)制程技术,预计第一批产品将在2024上半年登场。

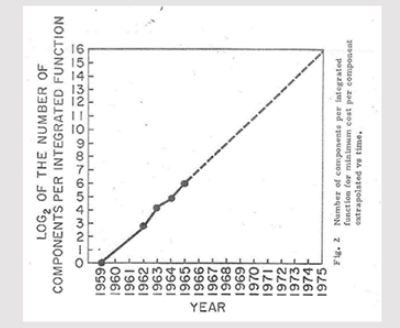

据了解,Intel创始人戈登·摩尔曾提出摩尔定律,其核心内容为:集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。

虽然随着晶体管内嵌晶体管数量越多,难度指数被上升,也有很多人对“摩尔定律”的可行性抱有怀疑态度,但由此来看,Intel仍是摩尔定律的坚定支持者。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论