凡亿教育-雯雯

凡事用心,一起进步打开APP

公司名片TMS320C54x DSP芯片的结构分析

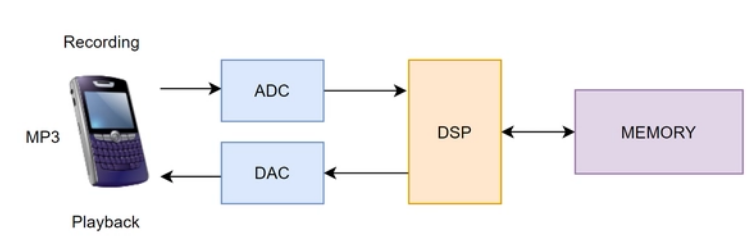

随着时代发展,DSP芯片已成为主流的芯片之一,更是随着数字系统的兴起,迎来黄金发展期,作为常见的DSP芯片,TMS320C54x已成为电子工程师必须重点了解的DSP芯片之一,今天我们来看看TMS320C54x DSP芯片的结构。

TMS320C54x系列是针对低功耗、高性能的高速实时信号处理而专门设计的定点DSP,广泛应用于无线通信系统设备。

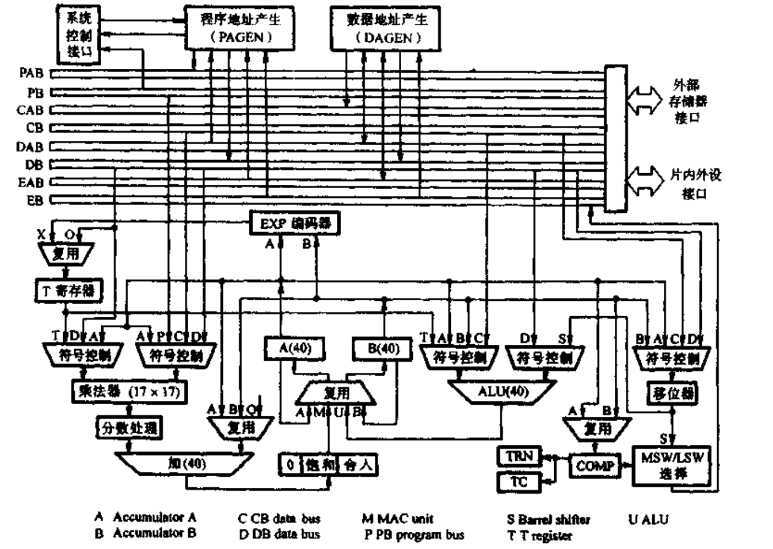

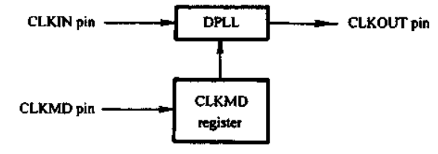

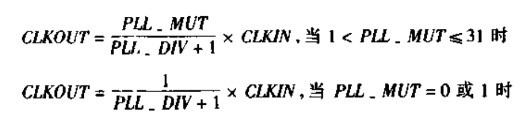

C54x系列定点DSP的CPU结构如图所示。C54x系列的DSP CPU具有以下特征:

1、采用改进的哈佛结构,一条程序总线(PB)、三条数据总线(CB、DB、EB)和四条地址总线( PAB.CAB,DAB 、EAB),提高了性能和操作的灵活性。

2、40比特的算术逻辑单元(ALU)以及--一个40比特的移位器( shifter)和两个40比特的累加器(A、B),支持32比特或双16比特的运算。

3、17×17比特的硬件乘法器和·个40比特专用加法器的组合(MAC)可以在一个周期内完成乘加运算,速度非常快。

4、比较、选择和存储等单元能够加速Viterbi译码的执行。

5、专门的指数编码器(EXP encoder)能够在一个周期内完成累加器中40比特数值的指数运算。

6、单独的数据地址产生单元(DACEN)和程序地址产生单元( PAGEN),能够同时进行个读操作和一个写操作。

7、这种优化的结构,使C54x能在不引起硬件资源的冲突下支持--定的指令并行,如读操作数和写操作数的同时执行,读操作数和乘法的同时执行等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论