凡亿教育-雯雯

凡事用心,一起进步打开APP

公司名片集成电路如何减小寄生电容?

寄生电容在集成电路是无处不在,但若电路设计对电容敏感度低可忽略寄生电容带来的影响,但若电路设计要求芯片速度快或频率高,寄生电容将十分重要,所以若是遇见这个情况,该如何减小寄生电容带来的影响?

首先需要知道的是,若模拟电路频率一旦超频率20MHz以上,就必须时刻对寄生电容保持关注。否则他很有可能将毁掉整个芯片。减少寄生电容的影响可从以下几方面入手:

1、导线长度

若集成电路某个区域的寄生参数必须要小,最直接最有效的方法是缩短导线长度,因为减少了导线的长度就是减少了导线和衬底或导线和别的导电层之间的重叠。与它作用相关而产生的电容,如金属或衬底层的电容将会相应地减少。

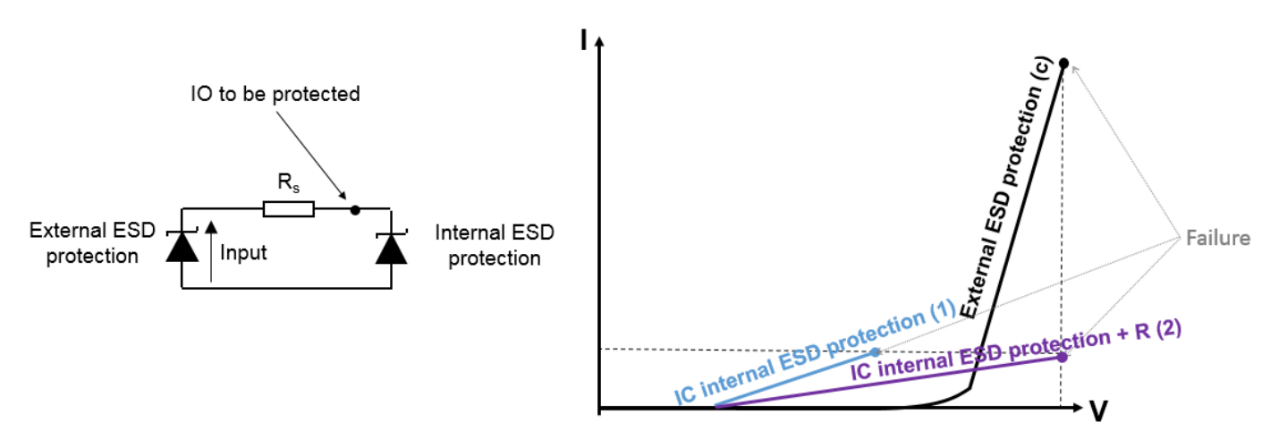

2、选择金属层

该种设计方法其主要作用的是衬底和导线间的电容,所以选用金属电容最小的金属层即可。通常情况下,最高金属层所形成的的电容是最小的,电容大小与平板的间距成反比

3、金属叠着金属

在某些电路的上面布置金属线,这是在数字自动布局布线中经常会遇到的情况。各层金属相互交叠,所以在反相器、触发器等都存在寄生电容。如果不加以干预的话,只是由布线器来操作,那么就有可能毁了芯片。在模拟电路版图设计中,工程师经常会人为的将敏感信号隔离开来,尽量避免在敏感电路上面走线,而只是将金属线走在电路之间,这样寄生的参数就小一些且相对容易控制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论