信号完整性(SI)及管道完整性(PI)仿真模拟是很多小白最为头痛的高速PCB设计问题,也是很多工程师花很多时间去巩固学习的知识点内容,今天就讲讲电路有哪些因素是会影响到信号完整性。

一般来说,信号完整性是指信号在信号线上的质量,信号具有良好的信号完整性是指当在需要时候,具有所必须达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的,特别是在告诉电路中,所使用的的芯片切换速度过快、端接与案件布设不合理、电路的互连不合理等都会引起信号的完整性问题,具体主要包括串扰、反射、过冲与下重、振荡、信号延迟等。

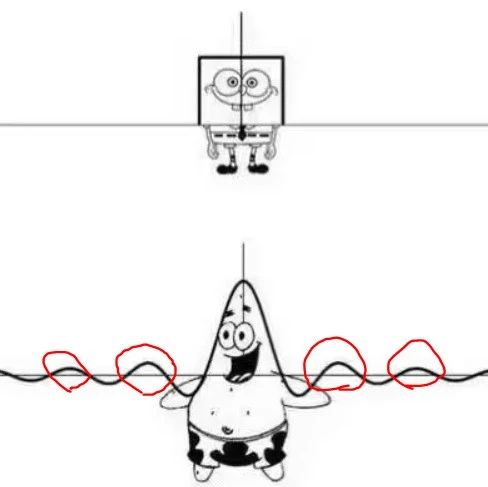

1、反射(Reflection)

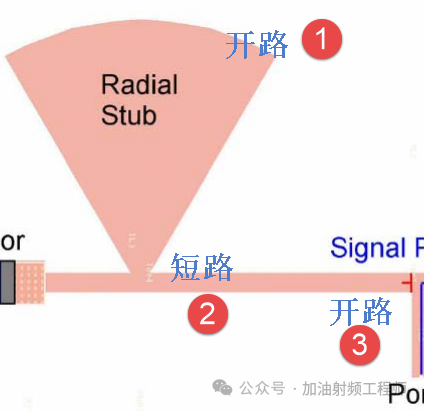

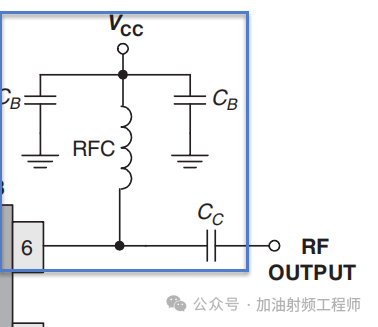

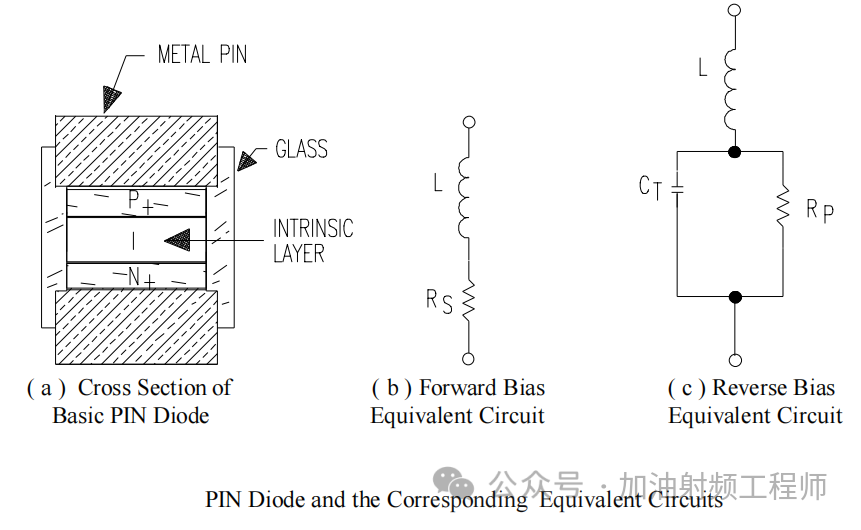

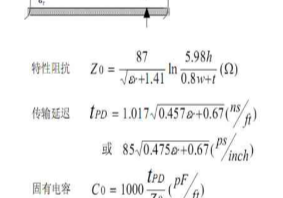

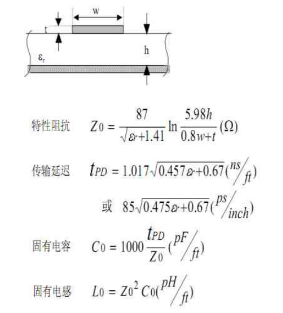

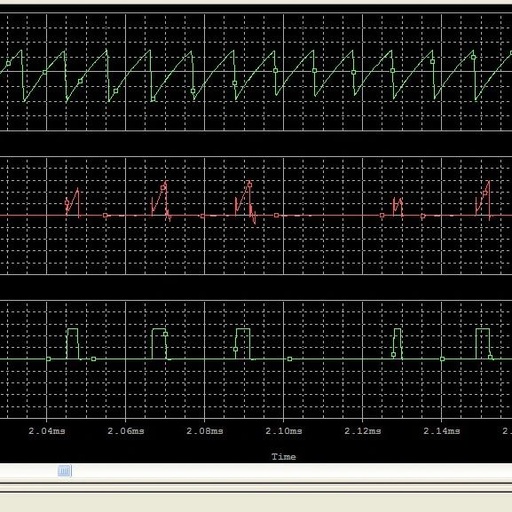

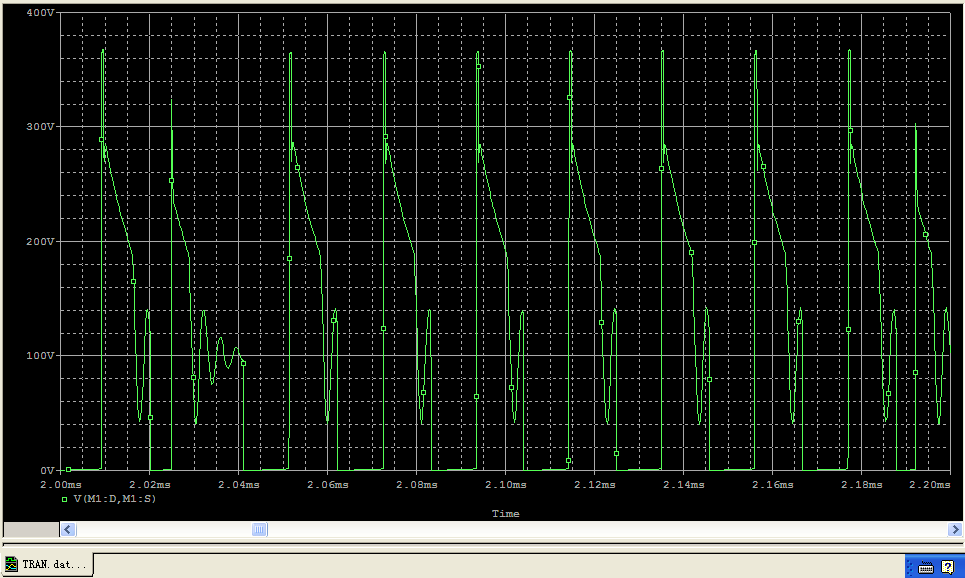

反射和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,就是信号在传输线上的回波现象。此时信号功率没有全部传输到负载处,有一部分被反射回来了。在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。如果在时钟信号上可能引起时钟沿不单调,进而引起误触发。一般布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素均会导致此类反射。另外常有一个输出多个接收,这时不同的布线策略产生的反射对每个接收端的影响也不相同,所以布线策略也是影响反射的一个不可忽视的因素。

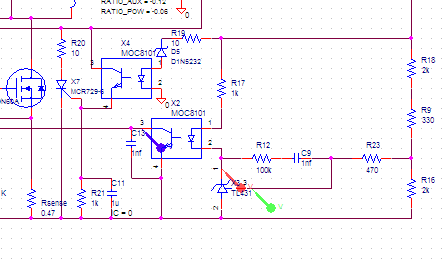

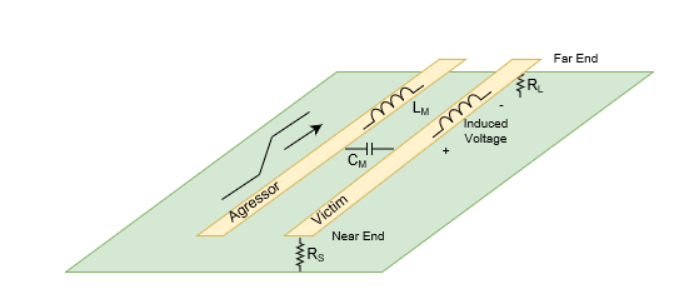

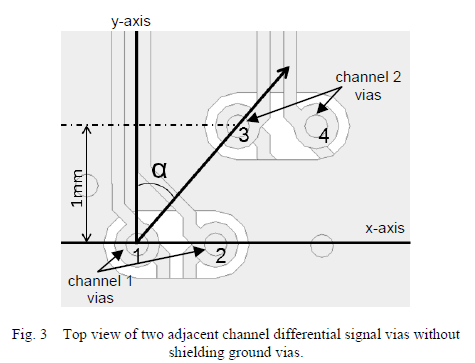

2、串扰(Crosstalk)

串扰是相邻两条信号线之间的不必要的耦合,信号线之间的互感和互容引起线上的噪声。因此也就把它分为感性串扰和容性串扰,分别引发耦合电流和耦合电压。当信号的边沿速率低于Ins时,串扰问题就应该考虑了。如果信号线上有交变的信号电流通过时,会产生交变的磁场,处于磁场中的相邻的信号线会感应出信号电压。一般PCB板层的参数、信号线间距、驱动端和接收端的电气特性及信号线的端接方式对串扰都有一定的影响。在Cadence的信号仿真工具中可以同时对6条耦合信号线进行串扰后仿真,可以设置的扫描参数有:PCB的介电常数,介质的厚度,沉铜厚度,信号线长度和宽度,信号线的间距.仿真时还必须指定一个受侵害的信号线,也就是考察另外的信号线对本条线路的干扰情况,激励设置为常高或是常低,这样就可以测到其他信号线对木条信号线的感应电压的总和,从而可以得到满足要求的最小间距和最大并行长度。

由于文章篇幅所限,将此文分为上下两篇,欲看下篇可点击《一文教你看懂信号完整性(SI)(下)》。

暂无评论