在IC设计阶段,为保证所设计的产品顺利上市,具有更高的竞争力,很多工程师会进行可测性设计确保无误,其中常用的方法莫过于基于JTAG的可测性设计,今天就给小伙伴们科普基于JTAG的可测性设计,希望能帮上忙。

JTAG,也叫做边界扫描BSD,最初是由欧洲测试工程师所提出的标准,这些测试工程师自称JETAG,后来美国工程师加入该组织,开始自称JTAG,JTAG组织提出一种技术,在芯片便捷加上串行移位寄存器,以实现对芯片的测试,该技术叫做边界扫描。

若工程师决定采用便捷扫描技术,需要进行以下步骤:

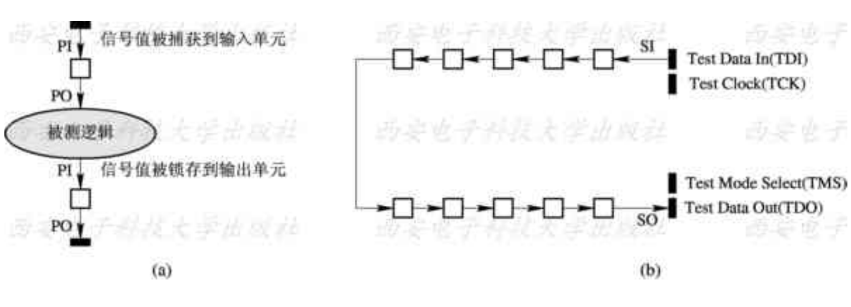

①将测试向量载入到便捷扫描单元地,此操作应串行完成。

②将边界扫描单元中的内容载入到设计中,此操作应并行完成。

③将设计的响应移入到边界扫描单元,此操作应并行完成、

④将响应从边界扫描单元移出去,此操作应串行完成。

为了使边界扫描单元构成的扫描链能支持串行输入/串行输出、并行输入/并行输出,边界扫描单元应具有串行输入端口(用SI表示)、串行输出端口(用SO表示)、并行输入端口(用PI表示)和并行输出端口(用PO表示)。同时边界扫描单元的具体构造跟它能完成的功能有关。

在JTAG标准中,还加入了TMS端口。它有什么用处呢?

TMS即测试模式选择(Test Mode Select) , 用于控制测试模式

实际上,不要仅仅将JTAG看作是一个由边界扫描寄存器组成的串行边界扫描链。 JTAG定义了许多非常灵活的功能。 如在一个由多个IC组成的板级系统中,JTAG可检查其中某一个芯片的引脚连接性而忽略其他芯片。

具体地说,由TMS端口输入的控制信号影响JTAG控制状态机,从而影响边界扫描链的功能。这样,在JTAG中,除了边界扫描链,还需要状态控制器 (TAP),用来控制JTAG口的状态。

除了边界扫描链和TAP控制器,在一个JTAG结构中,还包括以下寄存器:

旁路寄存器 (bypass register)

指令寄存器 (instruction register)

标识寄存器(identification register)

暂无评论