凡亿教育-佳佳

凡事用心,一起进步打开APP

公司名片触发器发生亚稳态后的状况及输出值参考

在数字IC系统设计时,触发器若是设计不当很容易出现,但很多小白都不知道触发器发生亚稳态后的输出情况,所以今天就讲讲,希望对小伙伴们有所帮助。

一般来说,若数字系统只存在逻辑,那么工程师也就不会面临可靠性的问题,然而、实际上,所有逻辑电路处理的是模拟电压信号,可靠性问题实际上来源于数字地电路的模拟特性。

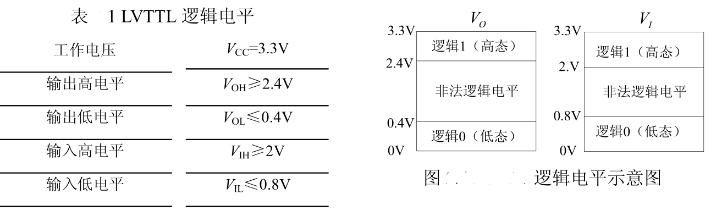

对于输出电平来说,大于VoH的电平将被解释为逻辑“1”,小于VoH的电平江北解释为逻辑“0”,介于VoH和VoL之间的电平属于非法逻辑电平;对于输入电平来说,大于VIH的电平将被截石位逻辑“1”,小于VIL的电平将被解释为逻辑“0”,介于VIH和VIL之间的电平属于非法逻辑电平。显然无论是输入电压还是输出电压,进行电平切换时,都将经历这段短暂的非法逻辑电平时间,以单触发器违例,发生亚稳态的触发器的输出情况可能有以下三种:

1、超过正常传播延迟但是没有超过一个时钟周期,输出稳定的逻辑值“1”,虽然可能与前级的输入值相反。

2、超过正常传播延迟但是没有超过一个时钟周期,输出稳定的逻辑值“0”,虽然可能与前级的输入值相反

3、在本次触发后的整整一个时钟周期都处于非法逻辑电平,直到下一次稳定的触发后进入稳态。

这 3 种情况对系统产生的影响正是本文讨论的内容,显然如果在由组合电路构成的反馈电路中出现了亚稳态,那么很容易波及到整个系统。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论