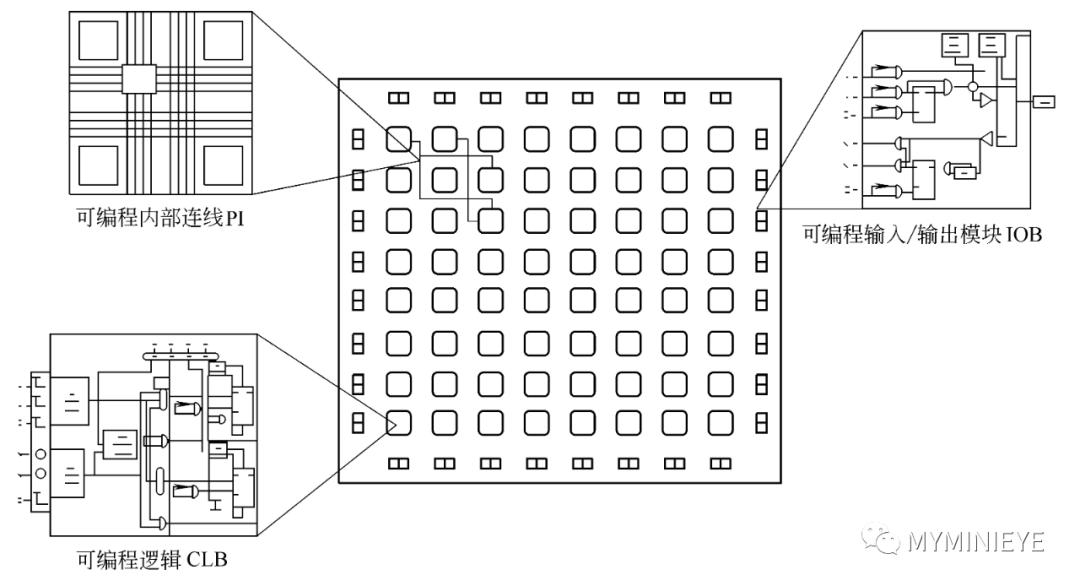

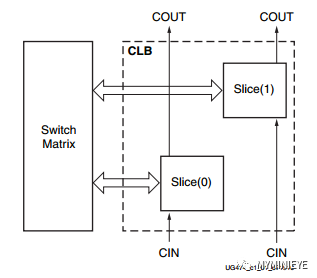

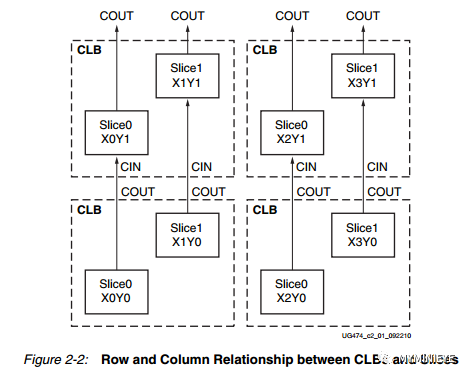

CLB是指可编程逻辑功能块(Configurable Logic Blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相同的SliceL或则一个SliceL和一个SliceM构成。每个Slice不仅可以用于实现组合逻辑、时序逻辑。其中,SliceM还可以配置为分布式RAM和分布式ROM。

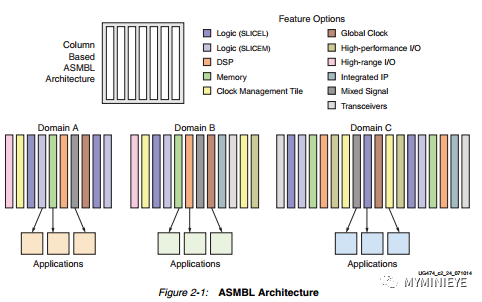

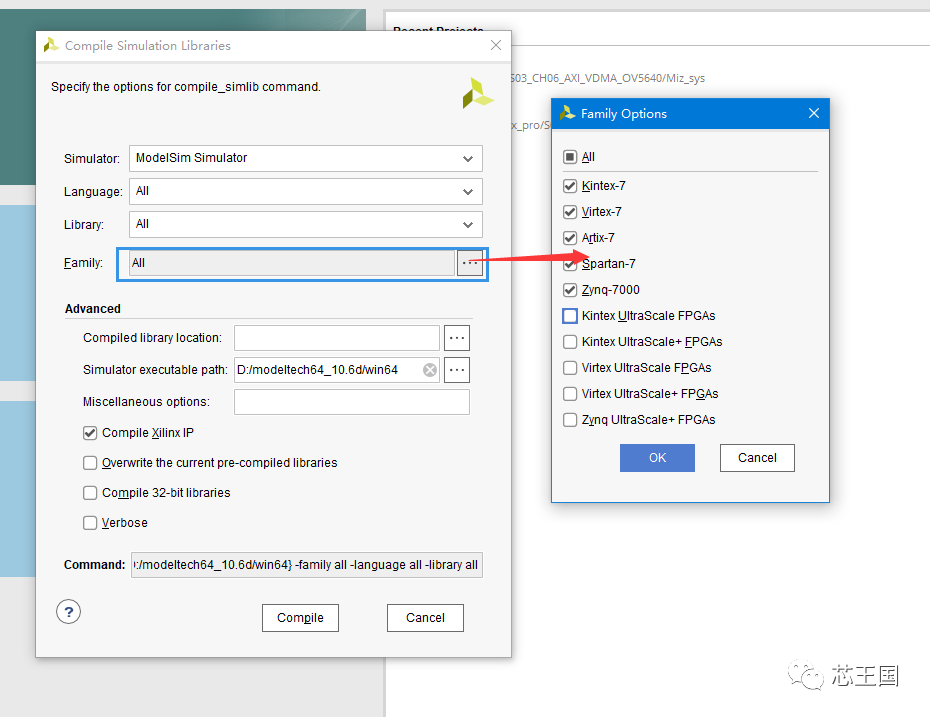

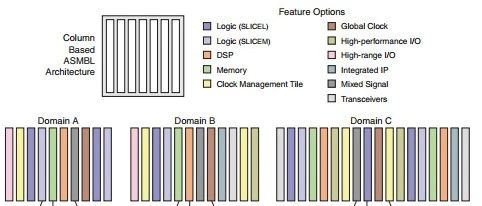

下面以Xilinx的ZYNQ的7000系列为例介绍其功能与结构

ZYNQ7000系列采用了Xilinx全新的第四代ASMBL架构。

新的架构优化了芯片布局,消除了IO数量增长带来的芯片阵列的尺寸约束;

新的架构能够满足在芯片的任何位置放置电源和地;

增加了更多电源和地;

允许多种完全不同功能的IP单元在芯片内独立排布;

独特的SSI技术;

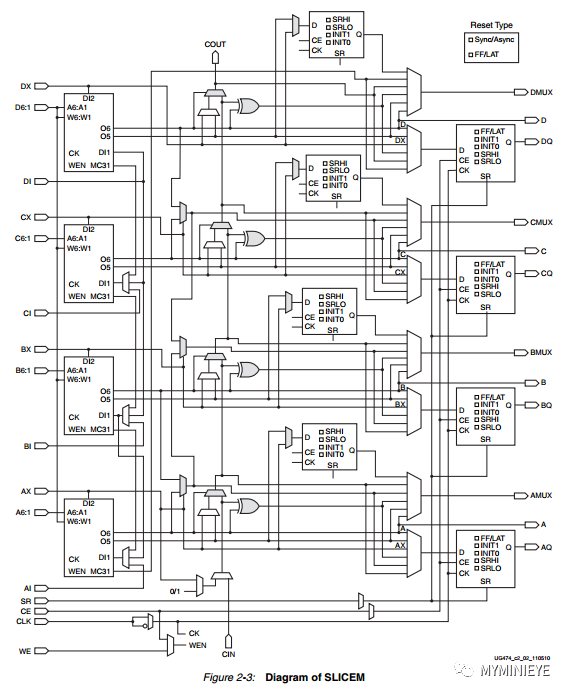

且分布式RAM和移位寄存器只能在SliceM中

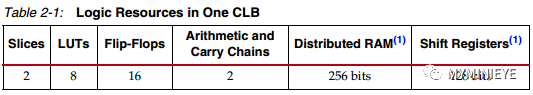

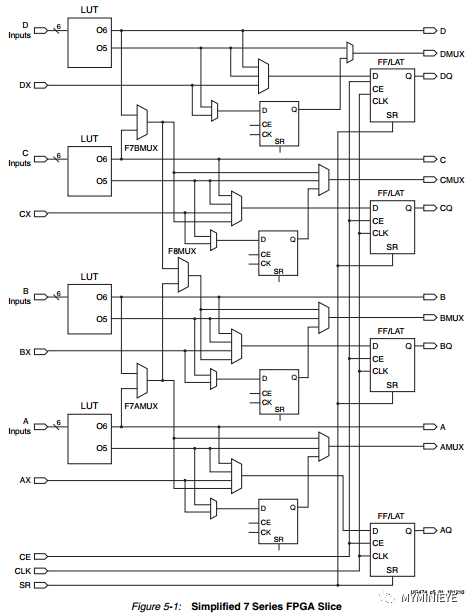

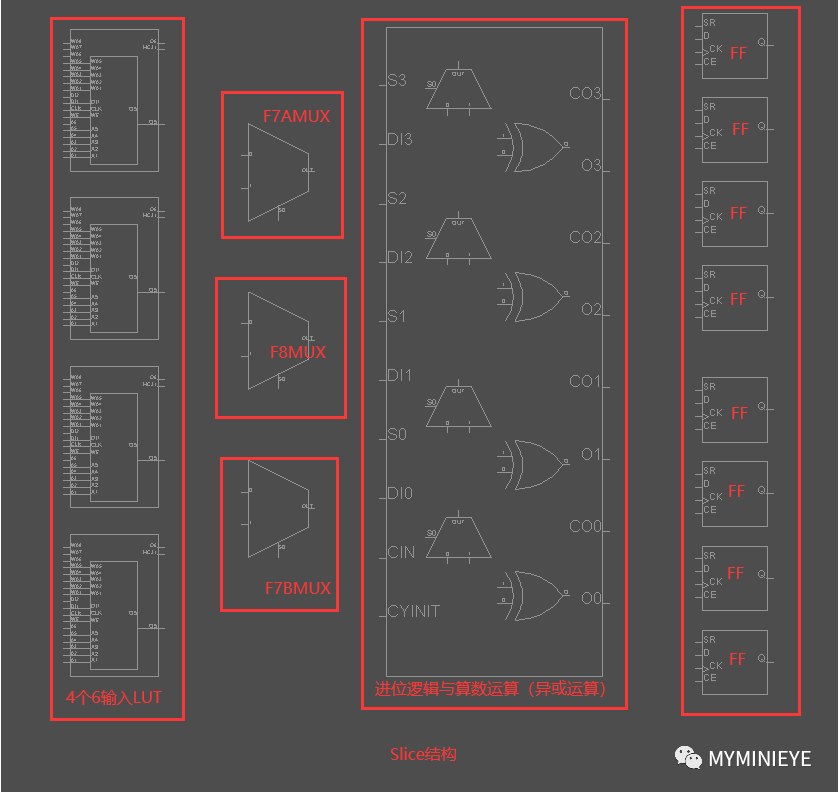

1.SLICE:(1Slice=4LUT+8FF)

Slice是Xilinx公司定义的基本逻辑单位,其内部结构如图1-4所示,一个Slice由四个6输入的LUTS、进位逻辑、算术逻辑、存储逻辑和多路复选器组成。算术逻辑包括一个异或门(XORG),一个异或门可以使一个Slice实现 2bit全加操作,专用与门用于提高乘法器的效率;进位逻辑由专用进位信号和函数复用器(MUXC)组成,用于实现快速的算术加减法操作;4输入函数发生器用于实现4输入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的两个输入函数为6输入,可以实现6输入LUT或 64比特移位寄存器);进位逻辑包括两条快速进位链,用于提高CLB模块的处理速度

每个Slice包含:

•四个6输入查找表LUT

•八个存储单元

•多路复选器

•进位逻辑

所有Slice均使用这些单元来提供逻辑,算术和ROM功能。在

此外,某些slice还支持两个附加功能:使用分布式存储数据

RAM和32位寄存器的移位数据。支持这些附加功能的slice

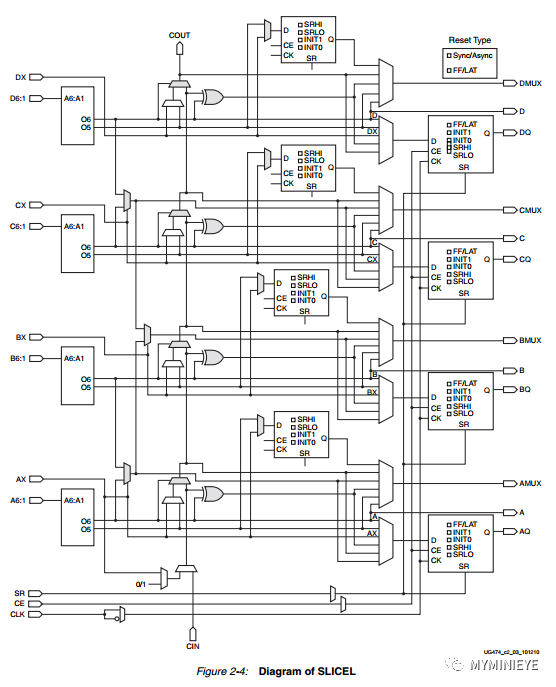

称为SLICEM;其他的则称为SLICEL。

SLICEL如图2-4所示。

每个CLB可以包含两个SLICEL或一个SLICEL和一个SLICEM。

Slices分为SliceL和SliceM,一般情况下,SliceL>SliceM数

2.LUT查找表

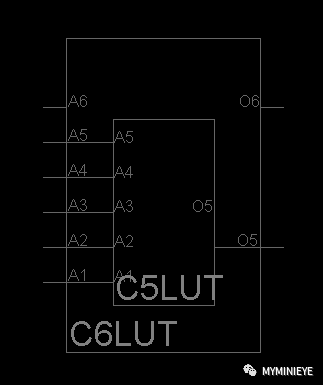

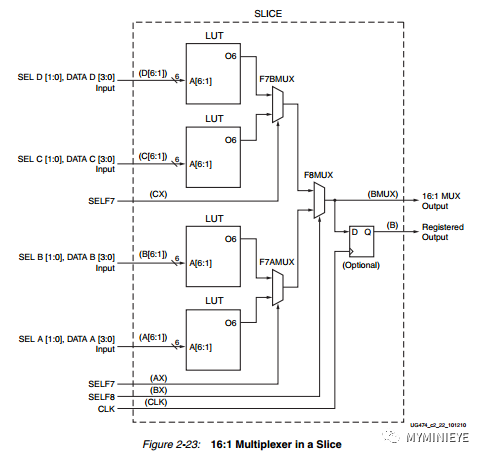

1个Slice包含4个6输入的LUT,两个LUT通过F7MUX进行级联可以形成一个7输入的LUT,1个Slice可以形成2个7输入的LUT;还可通过F8MUX进行级联形成一个8输入的LUT,逻辑资源换算关系:6输入查找表是4输入查找表的1.6倍查找表LUT本质是RAM,相当于一个多路选择器LUT可参与进位逻辑,进行算数运算单元进行异或运算等,也可直接输出。

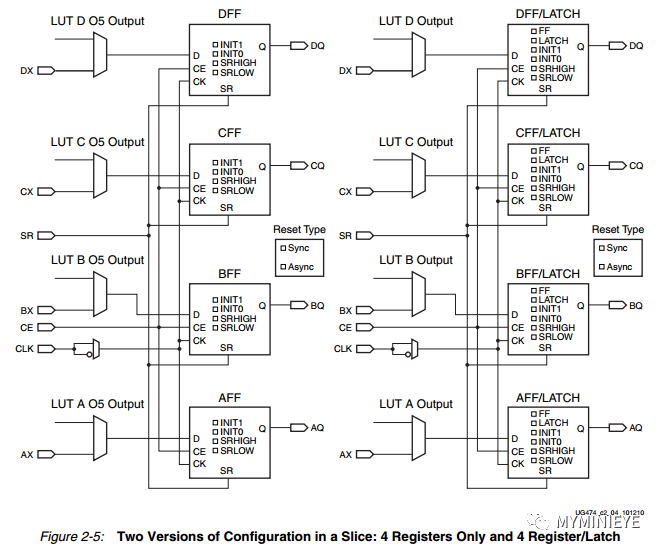

3.存储单元

每个Slice有8个存储单元,4个可配置成DFF或者锁存器,另外4个只能配置为DFF

控制信号

控制信号

而SliceL与SliceM最大的区别就是没有分布式RAM和移位寄存器。

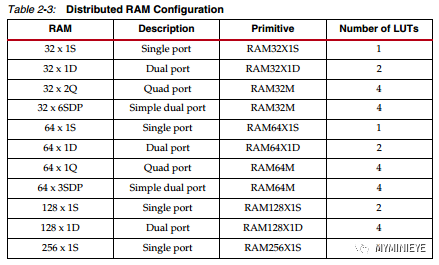

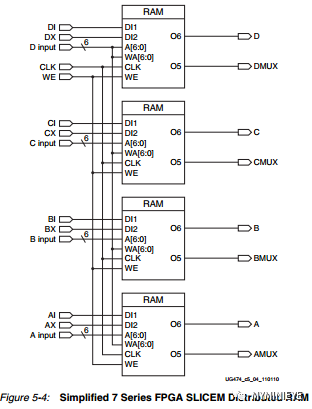

4.分布式RAM(仅限SliceM)

SLICEM可以配置成分布式RAM,多bit的情况需要增加相应倍数的LUT进行并联。

分布式RAM比块RAM有更好的灵活性,但块RAM的资源比较宝贵,分布式RAM适用小规模存储场景。

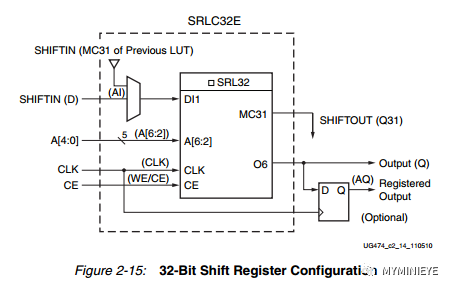

5.移位寄存器(仅限SliceM)

SLICEM在不使用触发器的情况下可以设置成32bit的移位寄存器,4个LUT可级联成128bit的移位寄存器。SliceM之间级联还可形成更大的移位寄存器

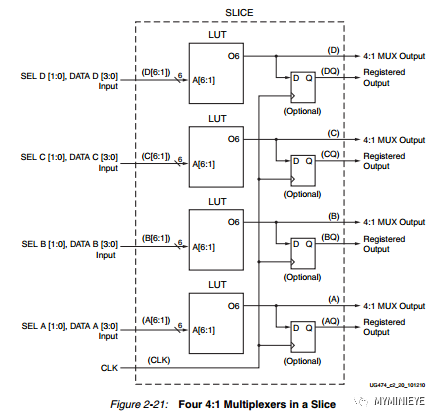

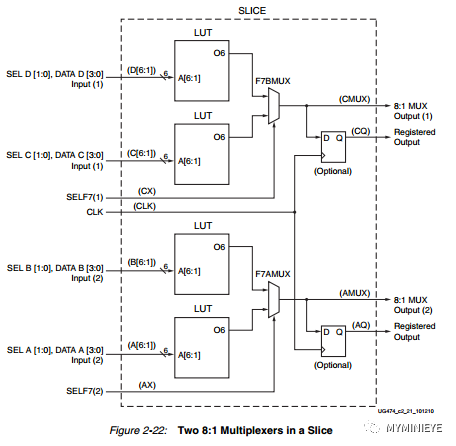

6.多路复选器MUX

1个LUT可配置成4:1MUX

2个LUT最多可配置成8:1MUX

4个LUT最多可配置成16:1MUX

也可通过布线资源连接多个Slice形成更大规模的设计

但会占用布线资源,产生较大延迟

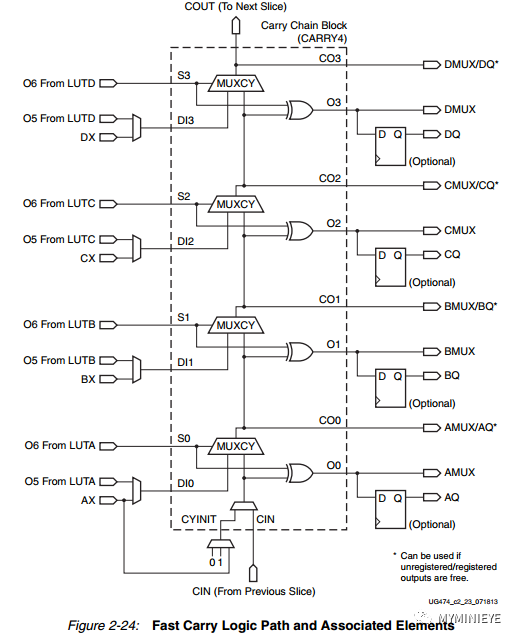

有两条快速进位链,它与本列的上下slice的进位链相连,实现数据运算时的进位操作,每个slice有4bit 的进位链,每bit都由一个进位MUX和一个异或门组成

可实现加法/减法器时生成进位逻辑,也可产生一般逻辑。

暂无评论