采用Chiplet的设计方式已是大势所趋,但究竟何时会开始大规模转向这种设计方法,目前仍有待确定。

尽管如此,一些与技术和商业相关的最大障碍正在得到解决。虽然基于Chiplet的设计目前对于许多公司来说在经济上仍难以企及,但这种情况已开始发生变化。一个新兴生态系统的初步迹象已经显现。

不久前,芯片行业还认为,只有那些别无选择的公司才会使用Chiplet。这种设计方法被认为不合理的原因有很多,包括成本、性能以及增加的设计复杂性等。将芯片整合和集成到单片芯片上的趋势似乎是未来的发展方向。

但事实证明,这是一个错误的假设。与Chiplet相关的问题一个接一个地被解决,或者被证明是被夸大了。越来越多的人正在表明为什么越来越多的公司应该考虑采用分立式设计。

随着越来越多的公司采用Chiplet,情况也会变得更加容易,而且其优势也会变得更加明显。

软IP的最大优势之一在于,一家公司不再需要成为所有领域的专家。“如果我要设计一个SoC,我会安排人来做模拟设计,”Cadence SSG产品营销总监Mayank Bhatnagar表示,“他们可能很优秀,但当我的SoC完成后,他们就转而去做其他项目。他们最终无法成为某一特定设计的专家,因为他们一直在做不同的事情。现在,设想一下,如果有一家专注于特定设计的公司,或者一家规模较小的公司,专注于进行同一个设计,使用不同的工艺节点或不同的速度等级。产品质量会更好,这并非因为实现了完全相同的IP,而是因为IP本身由同一群人反复优化。当一个专用团队来完成IP的设计时,该IP会得到优化,他们知道自己拥有巨大的市场,因此可以投资聘请最优秀的人才来做这件事。他们拥有巨大市场的原因是,他们利用了这个拥有标准接口的市场,因此他们知道可以瞄准大多数使用其IP的用户。

就像任何技术进步一样,事物的发展有多种方式。“当我们谈论Chiplet和复用时,普遍的概念是,它们是强化的实体,”新思科技工程副总裁Abhijeet Chakraborty表示,“它们已经完全完成了所有工作,你只需要把它插上去,连接好所有东西,就可以开始使用了。”

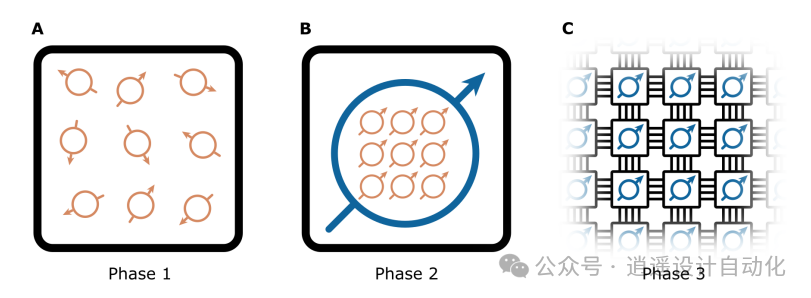

Chiplet的演进

上世纪90年代软IP的引入并不容易。推广之路艰难,而且缺乏相应标准。许多人曾怀疑它能否成功,因为它可能会造成效率低下。

Ansys产品营销总监Marc Swinnen表示:“从原则上讲,Chiplet的采用没有理由不能复制我们从用于SoC的IP发展的历程。虽然需要创建一些机械和热模型,而且会更加复杂,但我认为我们能够解决这个问题。这只是一个完成工作、就标准达成一致并进行测试的问题。回顾IP市场的早期,IP的最初实例是内部库。当时的公司使用自己的IP,并有自己的内部标准。所有这些都是专有的。商业IP需要一段时间才能流行起来,人们也需要一段时间才能信任来自外部的模块。Chiplet也将经历同样的情况。”

Chiplet行业仍处于早期阶段。“我开始看到一些客户正在开发他们自己的Chiplet,”NHanced总裁Robert Patti表示,“这些Chiplet与其他任何公司的都不兼容。这种使用情况将会持续增长,因为各大公司已经意识到将自己的ASIC芯片集成到Chiplet中的价值。这使他们拥有更大的优势。在HPC、计算集群、加速器,甚至与之相关的内存子系统等方面,人们都在沿着这条路走下去。虽然有一部分人非常专注于利用UCIe,但由于所需的开销,以及必须在一个相当小的节点上才能真正有效地利用UCIe,因此它将是一个利基市场,而不是一个广泛的大众市场。”

随着时间的推移,标准化将逐渐显现。“我们将看到一种趋势,即更加标准的定制设计,你可以为顶层的任何部分预先定义好封装,”Marvell技术副总裁兼定制解决方案首席技术官Mark Kuemerle表示,“底层芯片是最难的。顶层芯片相对容易,因为它只需要消耗电力,并且需要通道来传输数据。底层芯片才是关键所在,因为你必须对其进行调整。可以想象,对于某种类型的器件,你有一个标准化的封装,然后将其作为模板应用到底层芯片设计中,这样你就可以基于它进行设计。”

当然,事情并非如此简单。“它比我们这些年来熟知和喜爱的软IP要复杂得多,”新思科技的Chakraborty表示,“你不仅要考虑Chiplet本身的复杂性,还要考虑测试标准、接口、可靠性和安全性等所有这些因素都必须发挥作用。它必须采用不同的技术规则和参数进行设计,每种规则和参数都有不同的要求和挑战。电源传输非常重要,也是一个关键问题,Chiplet必须解决这个问题,包括它们如何接收来自系统的电源。我们讨论的是TSV和凸块电源就是为了满足电源需求。所有这些都必须得到处理。它们必须协同起来。”

尚不成熟的生态系统

此外,还有一些其他挑战。Cadence的Bhatnagar表示:“肯定有对Chiplet的需求。有需求,但没有供应。有些公司已经开始开发Chiplet,并将其作为商品出售,但这还处于非常初始的阶段。最大的障碍是所需的投资。创建任何一种Chiplet都需要很长时间,成本也相当高,而且你希望能够明确自己所瞄准的市场空间。鉴于标准在不断发展,无论特定Chiplet有多好,其市场规模究竟有多大并不明确。如果你无法占领任何市场,如果没有人能够使用你的Chiplet,那么开发它就毫无价值。”

有些组织可以帮助推动这一进程。“随着开放计算项目的Chiplet市场等计划的实施,Chiplet生态系统正在不断发展,”Rapidus设计解决方案的现场首席技术官Rozalia Beica表示,“这为设计人员和制造商提供了集中的资源平台,从而支持采用基于Chiplet的设计。”

尽管如此,要在这个领域占据一席之地,需要有接受Chiplet的能力以及采用Chiplet所带来的明确益处。西门子EDA中央工程解决方案总监Pratyush Kamal表示:“目前市场上有一些公司提供Chiplet。他们面临着来自大型垂直行业的竞争,要想取得成功,就需要带领行业走向开放的Chiplet经济。设计SoC的垂直行业公司目前有五个不同的组织来构建这些核心。如果可以减少对其中一个组织的需求,他们可以节省20%的一次性非重复性费用——即设计和流片芯片的费用。你可以从设计流程中去除这笔费用。从这个意义上说,这是一个巨大的机会。”

例如,Arm已开始提供预集成的强化IP模块,以加速Chiplet的采用。Arm汽车业务高级总监Christopher Rumpf表示:“验证成本正在急剧增加。解决这个问题的方法是使用计算子系统。工作负载和软件是实现差异化的关键。”

有些Chiplet比其他Chiplet更有意义。“我们将逐渐看到一种聚集效应,”Patti表示,“构建垂直领域Chiplet的公司会希望相互交流,他们会想要FPGA芯片。我预计我们将开始看到各种尺寸的FPGA芯片。我们真正需要的是相对较小的FPGA器件,用来连接来自30家不同公司、各自进行协议发明的非协同设计芯片。”

DRAM已开始展现出所需的生态系统,尤其是在高带宽内存(HBM)方面。“生态系统、易复用性和标准化问题必须得到解决,”Chakraborty表示,“这会产生成本,也存在组装方面的挑战。目前,他们有很多疑问。他们不清楚该怎么做,也不清楚它的可靠性如何。例如,如果采用堆叠芯片,他们担心散热问题。如果我有其他替代方案,是否值得冒所有这些风险?一旦整个行业能够助力推动这一进程,使其风险大大降低,让用户能够提前了解风险和挑战,并做出明智的决定。那么我们认为,除了HPC AI客户之外,更多的人将会采用Chiplet。这种情况是不可避免的。”

将2.5D扩展到3D

当性能成为最终目标时,Chiplet的采用会变得更加困难——尤其是在涉及3D集成时。“我们从未成功复用过Chiplet,因为它们之间联系太紧密了,”Marvell的Kuemerle表示。

虽然标准正在制定中,但很少有人遵守。“由于没有统一的规范,整个市场存在问题,”Patti表示,“从广义上来说,我喜欢那种简单的连线方式,但要把各种东西连接在一起,将会是一套混合的标准。事实上的标准在市场上出现还需要很长时间。我们目前有点停滞不前,但真正需要做这件事的人将推动它的发展。至于3D,情况就更加复杂了,因为3D除了物理协议之外,还涉及物理层面。”

要想成功,公司和产品必须完美结合。“有些系统是基于性能参数的,它们会不断地更新迭代,或者从一个架构过渡到另一个架构,”Chakraborty表示,“实现这些目标的唯一方法是从完整的系统视角重新设计所有内容。但很多应用并不需要这样做。你可以重复利用,因为这不仅可以降低成本,还能更快、更可预测地实现完整的解决方案。对于那些适合模块化和重用的应用来说,问题又回到了‘要实现这样的生态系统需要什么呢?’”

随着每个应用的出现,我们会学到更多,行业也会不断进步。“定制HBM是我能想到的最接近可复用3D设计的方法,”Kuemerle表示,“这是一个非常独立且众所周知的问题。如果我们添加钩子来与顶部的3D DRAM芯片堆栈通信,我们就可以将其视为一个IP块。如果我们设置好与顶层的那堆叠的DRAM裸片进行通信的接口,我们就可以把它当作一个IP模块来处理。我们还有其他与那堆叠的DRAM相关的东西,比如电源传输,我们必须在底层裸片上进行规划。但当我们考虑这个问题时,我们可以定义与顶层堆叠或者顶层的任何部件进行通信所需的所有东西,然后我们可以围绕这些进行设计,并在这个空间内做任何我们想做的事情。”

暂无评论