凡亿教育-可可

凡事用心,一起进步打开APP

公司名片台积电:3nm工艺下半年量产,2nm工艺2025年投产

众所周知,芯片行业存在一个定理,那就是摩尔定律,主要内容是集成电路上可容纳的晶体管数目在大约每18个月便会增加一倍。

掌握FPGA/IC工程师需要的核心技能,来凡亿教育!

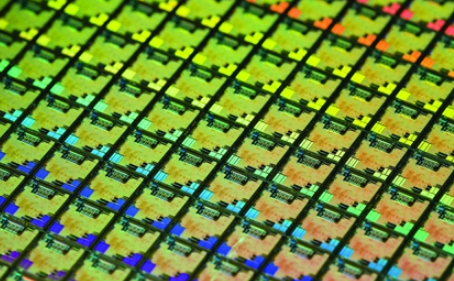

随着技术的提升和原材料的替代,各大企业的芯片工艺都在突飞猛进,其中以台积电、三星及英特尔为甚。以台积电为例,2018年台积电量产10nm工艺芯片,其晶体管密度是每平方毫米有0.53亿个;2019年台积电量产7nm工艺芯片,其晶体管密度是每平方毫米0.97亿个;2020年台积电量产5nm工艺芯片,其晶体管密度是每平方毫米1.73亿个。

到了2022年,台积电终于在4月14日第一季度电话会议上宣布3nm工艺芯片将在下半年量产,2nm工艺芯片最早在2025年投产。

台积电CEO魏哲家在该电话会议上回应了两个问题,一是关于台积电应对通货膨胀及整个经济形势的问题;二是有关台积电2nm工艺节点的时间表问题。魏哲家表示,台积电作为全球领先的代工企业,有能力应对市场波动。

同样,针对第二个问题,魏哲家表态,台积电2nm工艺正在研发中,有信心在2nm工艺依旧保持技术领先地位,该工艺将会在2024年开始预生产,于2025年正式投产。

据了解,台积电的2nm工艺将采用GAA FET(全环绕栅极晶体管)来替代finFET(鳍式场效应晶体管)。需要注意的是三星为与台积电竞争,以获取更多订单,率先在3nm工艺上采用GAA技术,英特尔计划在2024年改用GAA技术生产芯片,而台积电为保证芯片的效能及成本,选择finFET技术生产3nm工艺芯片。

欲了解更多的芯片资讯,来关注凡亿课堂。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论