凡亿教育-乐乐

凡事用心,一起进步打开APP

公司名片门阵列/标准单元/可编程逻辑器件是什么?

随着5G、物联网、人工智能等领域的快速并喷式发展,原本沉默平静的FPGA/ASIC芯片再度迎来了自己的春天。FPGA的开发涉及芯片和新架构、先进工艺、IP涉及及EDA工具开发等多方面,在FPGA的牵带下,ASIC芯片也重现辉煌,重回大众视野,然而部分小白依然不清楚ASIC芯片里的门阵列、标准单元、可编程逻辑器件是什么,所以本文将一一解答。

门阵列、标准单元、可编程逻辑器件都属于半定制ASIC。半定制ASIC是一种约束型设计方法,是指在芯片上制作好一些具有通用性的单元元件和元件组的半成品硬件,用户仅需考虑电路逻辑功能和各功能模块之间的合理连接即可,该半定制ASIC的优点是灵活方便,性价比高、明显缩短设计周期、提高了成品率。

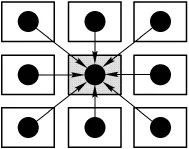

1、门阵列(Gate Array)

是指在硅片上制成标准的逻辑门,它是不封装的半成品,生产厂家可根据用户要求,在掩膜中制作出互连的图案(码点),最后封装为成品,在提供给用户。

2、标准单元(Standard Cell)

是指由集成电路厂家将预先设置好,经过测试且具有一定功能的逻辑块作为标准单元存储在数据库中,包括标准的TTL、CMOS、存储器、微处理器及I/O电路的专用单元阵列。设计人员在电路设计完成后,利用CAD根据在版图一级完成与电路一一对应的最终设计。标准单元设计灵活,功能强,但涉及和制造周期较长,开发费用也较高。

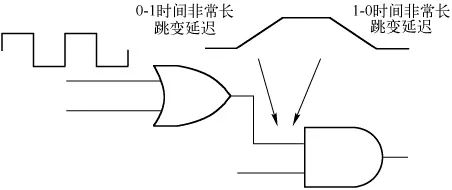

3、可编程逻辑器件(Programmable Logic Device)

属于ASIC的一个重要分支,是集成电路厂家作为一种通用性器件生产的半定制电路,用户可通过对器件编程实现所需要的逻辑功能。PLD是用户可配置的逻辑器件,成本较低,使用灵活,设计时发展非常迅速。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

进入分区查看更多精彩内容>

暂无评论