凡亿助教-小美

凡事用心,一起进步打开APP

公司名片STM32 走线与敷铜优化

浏览量:304

发布时间2023-09-01 17:32:17

10.11 走线与覆铜优化

处理完连通性之后,需要对走线和覆铜进行优化,一般分为以下几个方面。

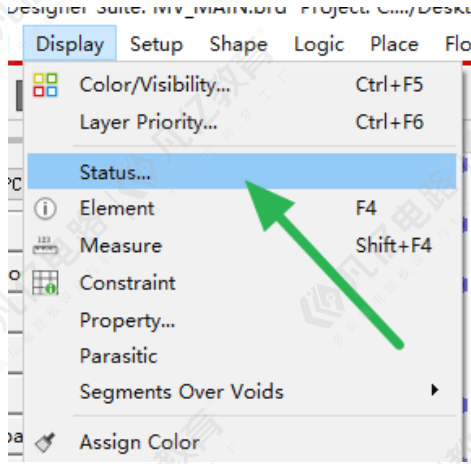

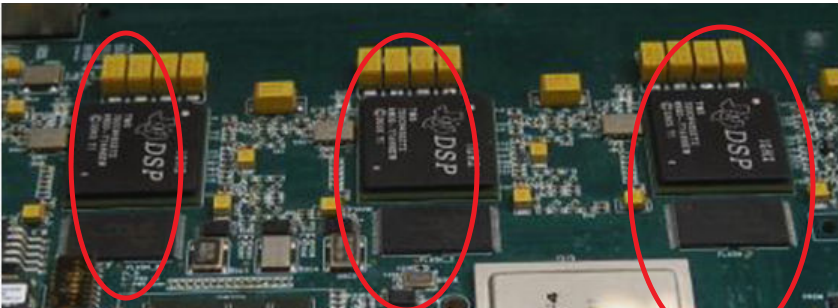

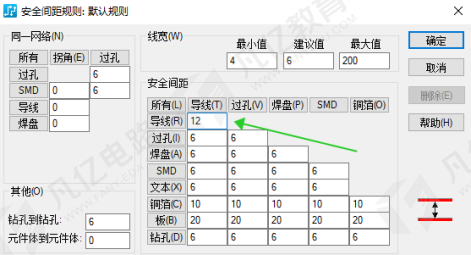

(1)走线间距满足3W原则。在走线时有时不注意,走线和走线太近,容易引起走线之间的串扰。处理完连通性之后,可以设置一个线与线间距的规则去协助检查,如图10-60所示。

10-60 布线规则设置

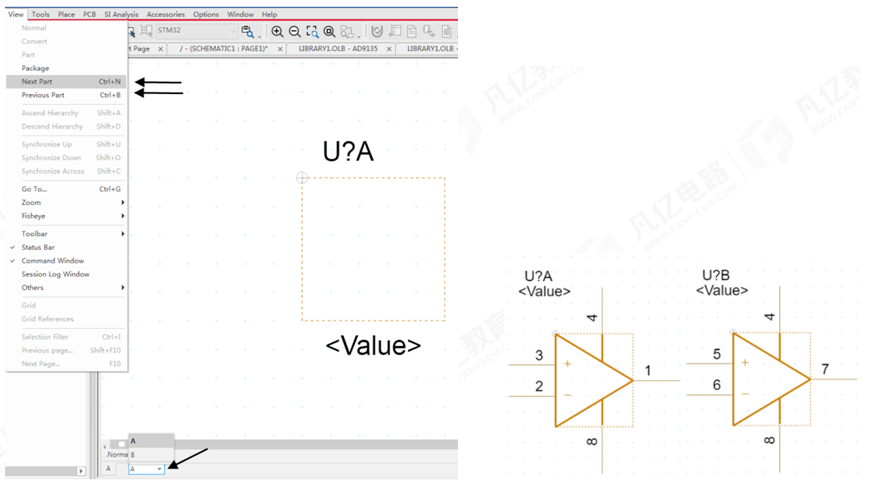

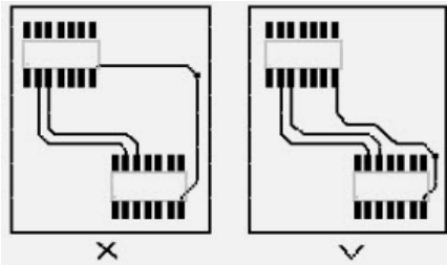

(2)减小信号环路面积。如图10-61所示,走线经常会包裹一个很大的环路,环路会造成对外辐射的面积增大,同样吸收辐射的面积也增大,走线优化的时候需要进行优化处理,减小环路面积,一般是按快捷键“Shift+S”单层显示之后人工检查。

10-61 布线环路检查

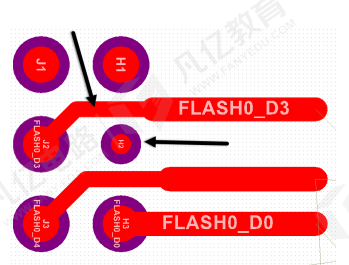

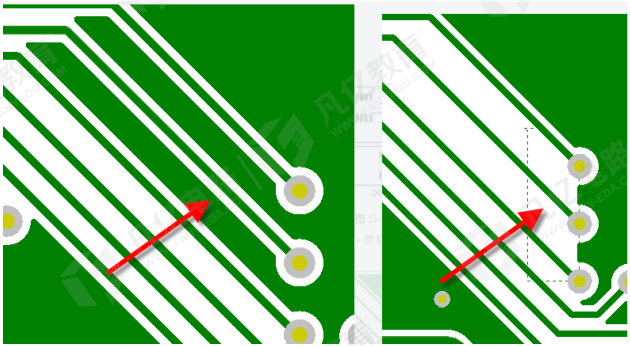

(3)修铜。主要是对一些电路瓶颈的地方进行修整,还有就是尖岬铜皮的删除,一般通过放置Cutout进行删除,如图10-62所示。

图10-62 铜皮处理

声明:本网站所收集的部分公开资料来源于互联网,转载的目的在于传递更多信息及用于网络分享,并不代表本站赞同其观点和对其真实性负责,也不构成任何其他建议。仅供学习交流使用,不构成商业目的。版权归原作者所有,如果您发现网站上有侵犯您的知识产权的作品,请与我们取得联系,我们会及时删除。

侵权投诉

下一篇 STM32 DRC检查