凡亿教育-婷婷

凡事用心,一起进步打开APP

公司名片PCB中差分蛇形等长的走线与设置

浏览量:1753

发布时间2023-12-22 14:39:20

至于USB、SATA、PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟包含在数据中发出,数据接收方通过接收到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制。

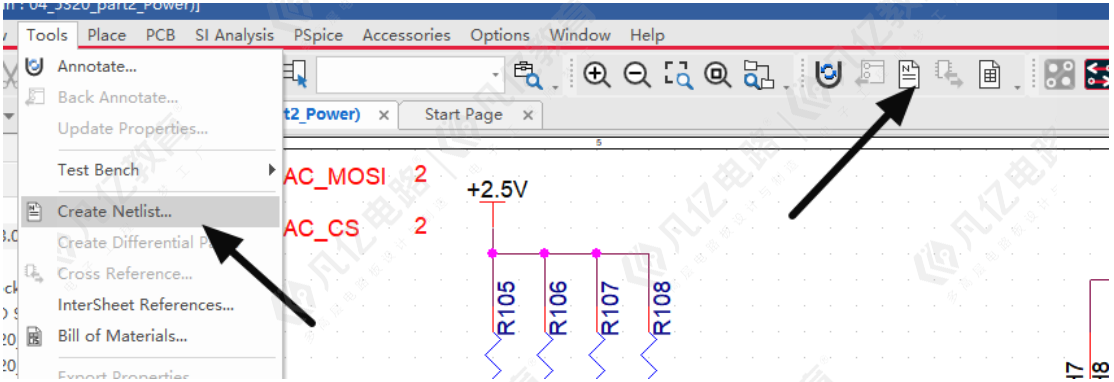

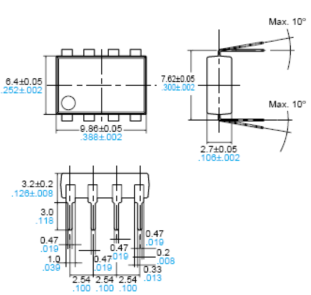

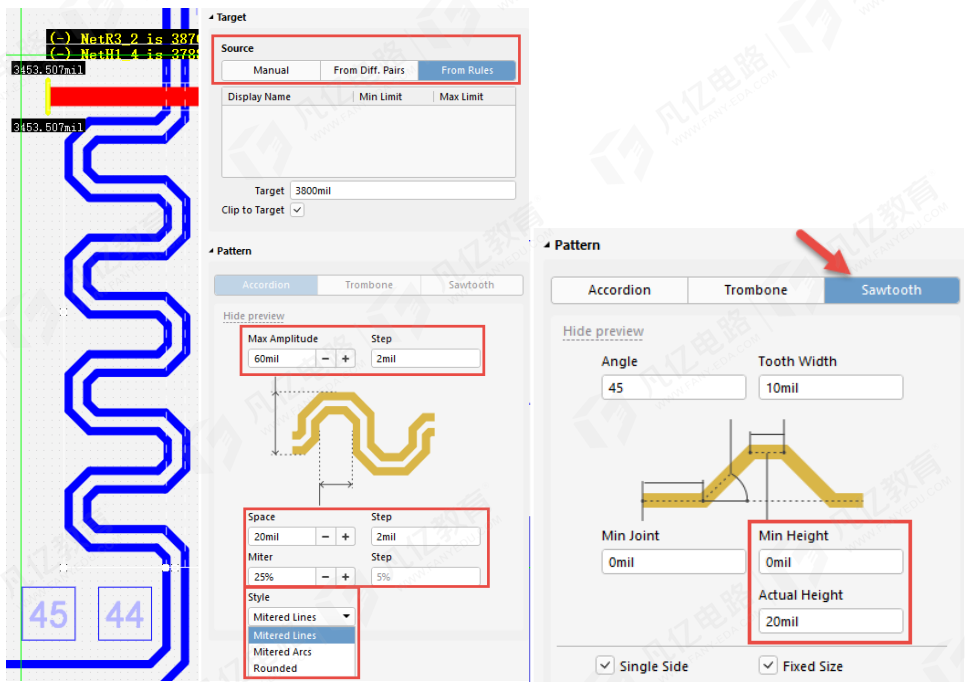

(1)差分蛇形线类似于单端蛇形线,也是先进行完差分走线,再执行菜单命令“布线-差分对网络等长调节”(快捷键“UP”),激活差分等长命令,单击需要等长的差分走线,并按“Tab”键调出类似于单端等长的参数设置窗口,如图10-111左图所示,按照要求设置差分蛇形线参数。

(2)单击需要等长的差分走线,并滑动鼠标,即开始差分蛇形走线,必要时也可以加阻碍线。

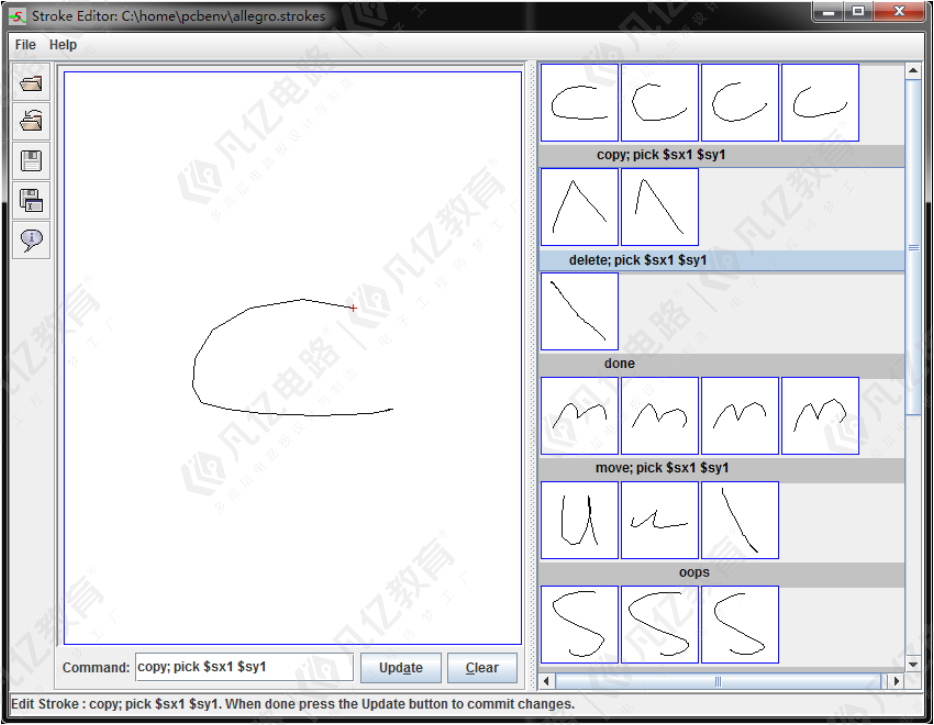

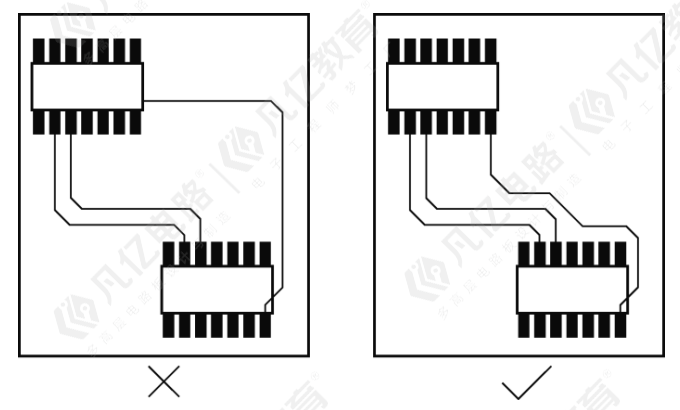

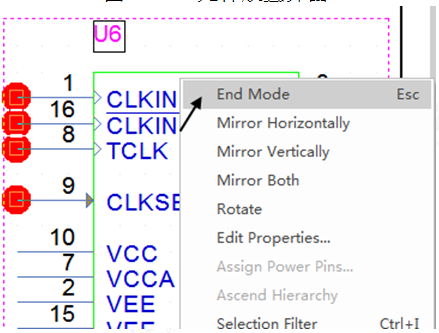

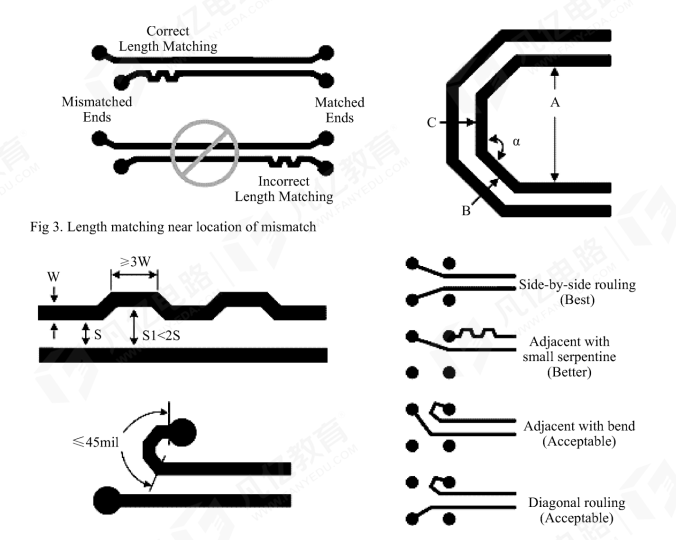

(3)为了满足差分对内之间的时序匹配,一般差分对内之间也需要进行等长,误差要求一般是5mil以内。这种等长方式一般不再是以差分走线来等长了,而是利用单端锯齿等长走线(快捷键“UR”时按“TAB”键选择“Sawtooth”模式),对差分走线的其中一条来进行锯齿等长。常见锯齿等长如图10-111右图所示,差分对内等长方式如图10-112所示。

图10-111 差分蛇形线参数设置及锯齿等长

图10-112 常见差分对内等长方式

声明:本网站所收集的部分公开资料来源于互联网,转载的目的在于传递更多信息及用于网络分享,并不代表本站赞同其观点和对其真实性负责,也不构成任何其他建议。仅供学习交流使用,不构成商业目的。版权归原作者所有,如果您发现网站上有侵犯您的知识产权的作品,请与我们取得联系,我们会及时删除。

侵权投诉