1、整体布线检查建议

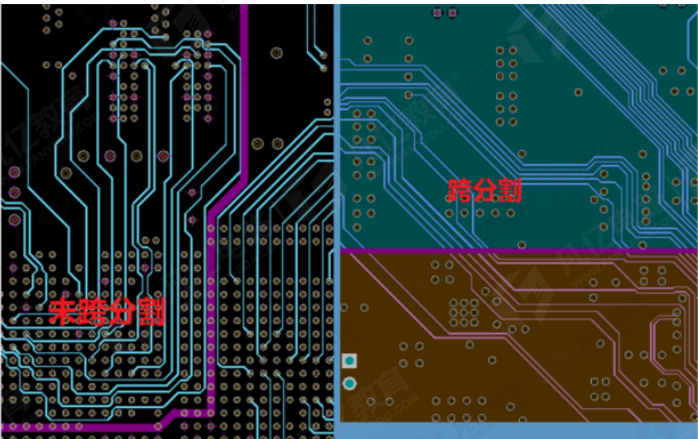

1)关键信号线走线避免跨分割

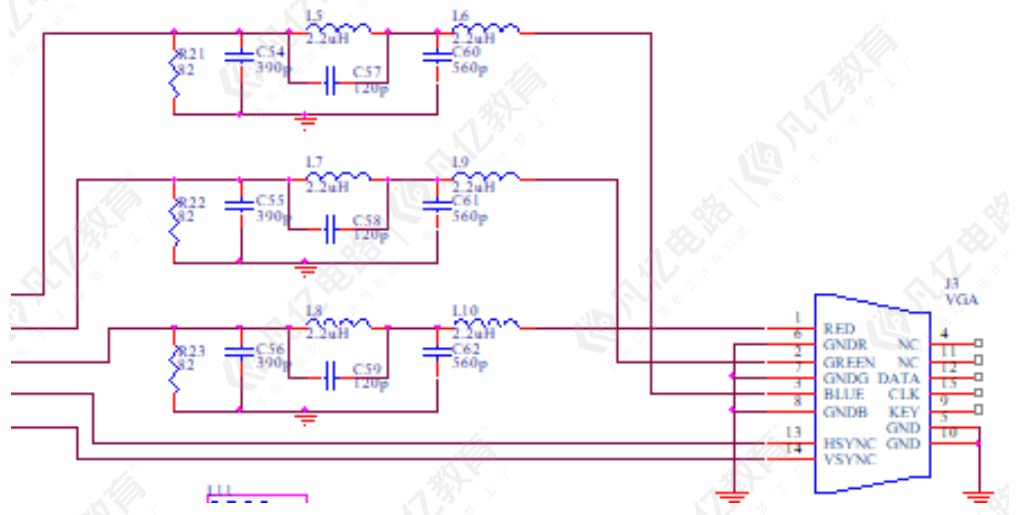

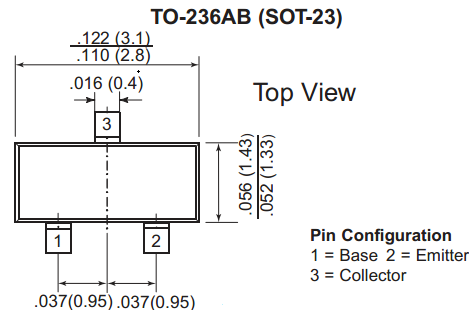

我们PCB中的信号都是阻抗线,是有参考的平面层,对于设计的关键信号避免跨分割的现象出现,否则会导致信号阻抗的突变,导致信号完整性问题的出现。如图9-10,描述了信号跨分割的现象。

图9-10 信号跨分割

2)相同功能的总线要并行走、中间不要夹叉其它信号,如果空间允许可以进行包地处理;

3)关键信号线走线避免“U”型或“O”型;

4)关键信号线走线不要人为的绕长(以最短路径进行走线);

5)关键信号线需要距离边沿和接口400mil以上;

6)晶振下面所有层都不能走线;

7)开关电源下面不能走线,特别是电感或转换芯片下方;

8)接收和发送信号要分开走,不能互相交叉布线。

2、隔离与保护

1)浪涌抑制器件(TVS管、压敏电阻)对应的信号走线尽量表层,短且粗(一般10mil以上);

2)不同接口之间的走线要清晰,不要互相交叉布线;

3)接口线到所连接的保护和滤波器件布线要尽量短;

4)接口线必需要先经过保护或滤波器件再到信号接收芯片;

5)接口器件的固定孔要接到保护地上,连接到机壳的定位孔、扳手要直接接到信号地;

6)变压器、光耦等器件的输入输出地要分开处理(两端使用不同的GND);

3、时钟布线

1)超过1inch的时钟线尽量走在内层,时钟线采用立体包地处理;

2)时钟线换层为不同的地参考平面需要增加回流地过孔;

3)时钟线不允许跨分割;

4)时钟线与其它信号线的间距达到5W,空间允许的情况下可以进行包地处理。

5)时钟电路的电源走线需要加宽或铺铜处理;

4、其他

1)保护地和信号地之间的间距大于80mil;

2)DC48V的爬电间距是否为80mil以上;

3)电源平面要比地平面内缩“20H”(H为电源和地平面的距离),一般情况地内缩20mil,电源需要内缩60mil,并间隔150mil打地过孔;

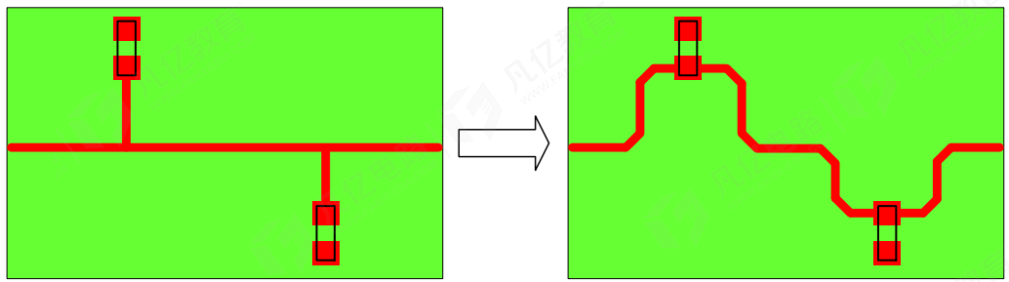

4)布线要避免出线Stub线,Stub线就是俗称的线头或歪线, 或者说信号没打算经过的路径;

5)AC220V的爬电间距最少为300mil,具体可以查爬电间距规格表;

6)差分走线可以抑制共模干扰;

7)敏感的信号线必须采用包地处理,包地线每隔200mil增加一个GND孔。